# CPU 8088

die PC- Baugrappe für den NDR- Computer

# (C) 1988 Graf Elektronik Systeme GmbH

Sämtliche Rechte - besonders das Übersetztungsrecht - an Text und Bildern vorbehalten. Fotomechanische Vervielfältigungen nur mit Genehmigung des Verlages. Jeder Nachdruck, auch auszugsweise, und jede Wiedergabe der Abbildungen, auch in verändertem Zustand, sind verboten.

# Wichtiger Hinweis

Die in diesem Buch wiedergegebenen Schaltungen und Verfahren werden ohne Rücksicht auf die Patentlage mitgeteilt. Sie sind ausschließlich für Amateur- und Lehrzwecke bestimmt und dürfen nicht gewerblich genutzt werden.

Alle Schaltungen und technischen Angaben in diesem Handbuch wurden von dem Autor mit größter Sorgfalt erarbeitet bzw. zusammengestellt und unter Einschaltung von wirksamen Kontrollmaßnahmen reproduziert. Trotzdem sind Fehler nicht ganz auszuschließen. Der Lizenzinhaber und der Autor sehen sich deshalb gezwungen, darauf hinzuweisen, daß sie weder Garantie noch die juristische Verantwortung oder irgendeine Haftung für Folgen, die auf fehlerhafte Angaben zurückzuführen sind, übernehmen.

#### 1.Ausgabe

Text: Klaus Bischof, Kempten GES

Gestaltung und Layout: Wolfgang Fink, Kempten GES Druck und Bindung: Druckerei Rieder, Kempten

Bestellnr.: 11267

Erstellt mit "MicrosoftWord" und "PageMaker" auf einem mc-modular-AT/386

| Inhaltsverzeichnis                                                                                                                                                                                                                                                                                                                                      | Seite                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 1.0 Einführung                                                                                                                                                                                                                                                                                                                                          | 6                                                              |

| 1.1 Zum NDR-Computer                                                                                                                                                                                                                                                                                                                                    | 6                                                              |

| 1.2 Entwicklung der CPU8088                                                                                                                                                                                                                                                                                                                             | 7                                                              |

| 1.3 Wie setzt man die CPU8088 ein                                                                                                                                                                                                                                                                                                                       | 10                                                             |

| 2.0 Technische Daten                                                                                                                                                                                                                                                                                                                                    | 12 .                                                           |

| 3.0 Prinzipbeschreibung                                                                                                                                                                                                                                                                                                                                 | 13                                                             |

| 3.1 Blockschaltbild                                                                                                                                                                                                                                                                                                                                     | 13                                                             |

| 3.2 Beschreibung des Blockschaltbildes 3.2.1 Die CPU 3.2.2 Der Coprozessor 3.2.3 Der "Adreßdemultiplex" 3.2.4 Der Bus-Controller 3.2.5 Die Speicher 3.2.6 Der Interrupt-Contoller 3.2.7 Timer 3.2.8 Die RESET- und Taktlogik 3.2.9 Die WAIT-Logik 3.2.10 Die Ein/Ausgabe 3.2.11 Der Keyboard-Controller 3.2.12 Die Select-Logik 3.2.13 Die Busanpassung | 14<br>14<br>14<br>14<br>15<br>15<br>15<br>16<br>16<br>16<br>16 |

| 4.0 Aufbauanleitung                                                                                                                                                                                                                                                                                                                                     | 18                                                             |

| 4.1 CMOS-Warnung 4.2 Stückliste                                                                                                                                                                                                                                                                                                                         | 18<br>18                                                       |

| 4.3 Aufbau Schritt für Schritt                                                                                                                                                                                                                                                                                                                          | 22                                                             |

| 5.0 | Testanleitung                              | 25 |

|-----|--------------------------------------------|----|

| 5.1 | Erste Prüfung ohne IC 's                   | 25 |

| 5.2 | Test im System                             | 26 |

|     | 5.2.1 Startkonfiguration                   | 26 |

|     | 5.2.2 Zum ersten Mal Einschalten           | 26 |

|     | 5.2.3 Vorbereitungen für MS-DOS            | 26 |

| 5.4 | Jumpereinstellungen                        | 27 |

| 6.0 | Anweisungen zur Fehlersuche                | 29 |

| 7.0 | Schaltungsbeschreibung                     | 31 |

| 7.1 | Der Prozessor                              | 31 |

| 7.2 | Die Statussignale                          | 31 |

| 7.3 | Der Coprozessor                            | 32 |

| 7.4 | Die Reset- und Taktlogik                   | 32 |

|     | 7.4.1 Der Takt                             | 33 |

|     | 7.4.2 Die Reset-Logik                      | 33 |

|     | 7.4.3 Das READY-Signal                     | 33 |

|     | 7.4.4 Das WAIT-Signal                      | 33 |

| 7.5 | Der Bus-Contoller                          | 34 |

| 7.6 | Der Daten- und Adressenmultiplex           | 35 |

| 7.7 | Der Decodier-/Select-Logik                 | 35 |

|     | 7.7.1 Die Select-Signale                   | 35 |

|     | 7.7.2 Die Portadressen                     | 36 |

|     | 7.7.3 Die Decodierung der Speicherbereiche | 37 |

| 7.8 | Der Interrupt-Controller                   | 38 |

|     | 7.8.1 Der Ablauf eines Interrupts          | 38 |

|     | 7 9 2 Die Beschaltung                      | 30 |

|                                               | GRAF     |

|-----------------------------------------------|----------|

|                                               | computer |

| 7.9 Der Timer                                 | 39       |

| 7.10 Die WAIT-Logik                           | 41       |

| 7.11 Die Busanpassung                         | 41       |

| 7.12 Die Adreßpuffer                          | 42       |

| 7.13 Der Keyboard-Controller                  | 42       |

| 7.13.1 Die parallele Ein/Ausgabe              | · 42     |

| 7.13.2 Das Einlesen eines Zeichens            | 44       |

| 8.0 Anwendungen                               | 46       |

| 8.1 Anwendung als Systembaugruppe             | 46       |

| 8.2 Anwendung als Single Board Computer (SBC) | 46       |

| 9.0 Kritik, Verbesserungen                    | 47       |

| 9.1 Verbesserungsvorschläge                   | 47       |

| 9.2 Updates zum BIOS                          | 47       |

| 9.3 Kritik                                    | 47       |

| 10.0 Bauelemente                              | 48       |

| 10.1 TTL Baustein                             | 48       |

| 10.1.1 74 LS 245                              | 48       |

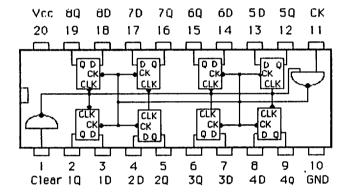

| 10.1.2 74 LS 322                              | 49       |

| 10.1.3 74 LS 373                              | 50       |

| 10.2 PALs                                     | 51       |

| 10.2.1 PAL1                                   | 51       |

| 10.2.2 PAL2                                   | 52       |

| 10.2.3 PAL3                                   | 53       |

| 10.2.4 PAL4                                   | 54       |

| 10.2.5 PAL5                                   | 55       |

# GRAF

| 10.3 Bausteine der Intel-82xx-Reihe                       | 56 |

|-----------------------------------------------------------|----|

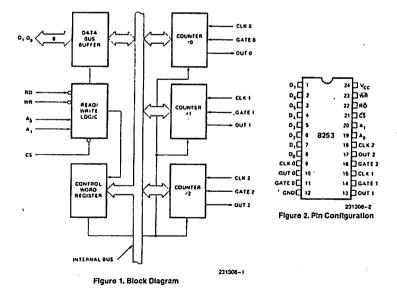

| 10.3.1 8253                                               | 56 |

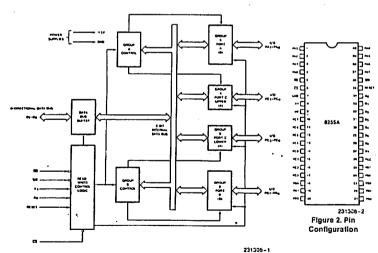

| 10.3.2 8255                                               | 56 |

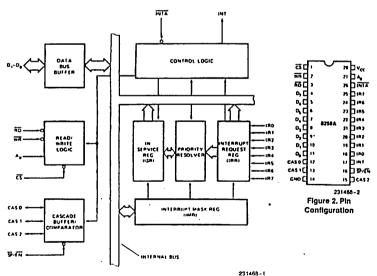

| 10.3.3 8259                                               | 58 |

| 10.3.4 8284                                               | 59 |

| 10.3.5 8288                                               | 60 |

| 10.4 Prozessor 8088                                       | 61 |

| 10.5 EPROM, RAM                                           | 87 |

| 10.5.1 27128                                              | 87 |

| 10.5.2 84256                                              | 88 |

| Anhang A: Schaltplan                                      | 89 |

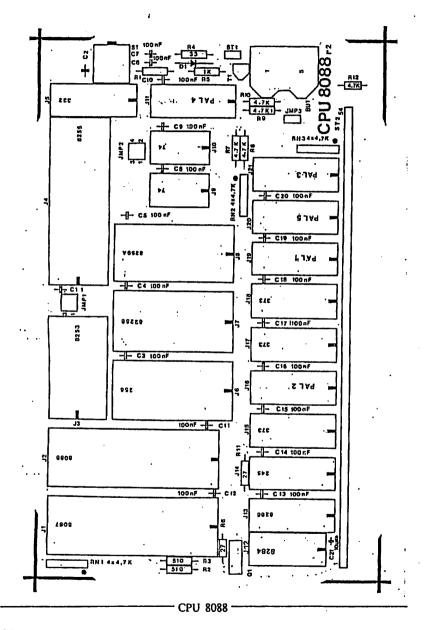

| Anhang B: Layout Bestückungsseite mit Bestückungsaufdruck | 90 |

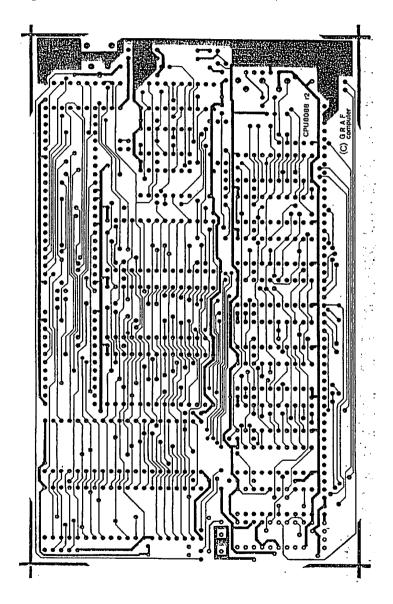

| Anhang C: Layout Bestückungsseite                         | 91 |

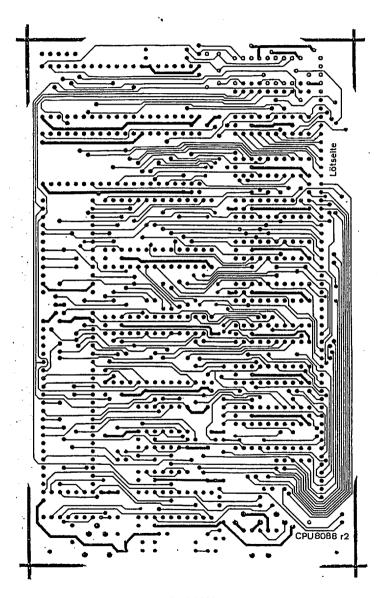

| Anhang D: Layout Lötseite                                 | 92 |

| Belegung der NDR-ASCII Tastatur beim CPU8088 BIOS         | 93 |

| 1. Standardebene                                          | 94 |

| 2. Zweite Ebene                                           |    |

| (vor jedem Zeichen CTRL "Klammeraffe" drücken)            | 95 |

| Erläuterungen zum RIOS VI 3                               | 06 |

# 1. Einführung

# 1.1 Zum NDR-Computer

Der NDR-Computer wird in der Fernsehserie "Rechner modular" aufgebaut, erklärt und in Betrieb genommen. Diese Serie wird vom Norddeutschen Rundfunk, vom Sender Freies Berlin, vom Bayerischen Fernsehen und von Radio Bremen ausgestrahlt. Der NDR-Computer wurde für diese Sendereihe entwickelt. Von Anfang an wurde bei diesem Computer das modulare Konzept in den Vordergrund gestellt. Mittlerweile laufen auf dem NDR-Computer nicht weniger als sechs CPUs und fünf Betriebssysteme. Kein anderes Computersystem kann eine solche Universalität aufweisen. Nähere Angaben zum modularen Konzept und zu den verfügbaren Baugruppen zum NDR-Computer finden Sie in unserem Farbkatalog mit über 200 Seiten.

Zur Serie gibt es einige Begleitmaterialien, daher ist es nicht unbedingt notwendig, die Fernsehserie gesehen zu haben, um den NDR-Computer zu bauen und zu begreifen:

- Buch: Rolf-Dieter Klein,

"Rechner modular"

ISBN 3-7723-8721-7, DM 68,-

erschienen im Franzis-Verlag, München

Bestellnummer: 10 991

- Sonderhefte der Zeitschrift "mc":

"Mikrocomputer Schritt für Schritt"

Bestellnummer: 10 399

"Mikrocomputer Schritt für Schritt Teil 2"

Bestellnummer: 10 398

- Zeitschriften: "mc" und "ELO" des Franzis-Verlags

- Zeitschrift: "LOOP" der Finna Graf Elektronik Systeme GmbH

Die Zeitschrift LOOP ist eine Kundenzeitschrift und enthält Neuerungen, Änderungen, Tips und Tricks, Software usw. zum

NDR-Computer und auch speziell zu dieser Baugruppe.

Viedeokassetten:

lizensierte Original-Kassetten für den privaten Gebrauch. Auf diesen Kassetten sind die 26 Folgen der Fernsehserie enthalten.

System:

VHS zwei Kassetten Bestell Nr.: 10 439 VIDEO 2000 Bestell Nr.:10 438

# 1.2 Entwicklung der CPU8088

Bei der Entwicklung der CPU8088 war uns von Anfang an klar, daß diese nur dann sinnvoll ist, wenn der NDR-Computer damit kompatibel zum IBM-PC wird. Doch dies schien noch vor einigen Jahren ein Ding der Unmöglichkeit. Viele Hersteller bemühten sich damals den IBM-PC möglichst mit identischer Hardware nachzubauen. Dies war natürlich für den NDR-Computer nicht möglich.

Hier wäre das modulare Konzept des NDR-Computers in einer Sackgasse gelandet.

Mit diesem Zustand waren wir natürlich nicht zufrieden und stellten Überlegungen an, wie die Baugruppen des NDR-Computers weiter verwendet werden könnten und der NDR-Computer dennoch IBM-kompatibel gebaut werden könnte.

#### Wir haben es geschafft!

Wir haben uns überlegt, was ein PC unbedingt benötigt, und was durch das BIOS (das Betriebsprogramm eines IBM-Rechners) anpaßbar wäre. Bei den Schnittstellen für Graphik, Festplatte, Laufwerke und Speichern konnten wir durch "jonglieren" auf die hardwarekompatiblen Bausteine verzichten. Nicht so bei den Bausteinen für Interrupt, Timer, Parallelbaustein und DMA. Diese Bausteine mußten möglichst auch beim NDR-Computer verwendet werden, d.h. die entsprechenden Bausteine müssen direkt auf die CPU-Karte oder auf einer neuen Karte untergebracht werden. Diese komplette Schaltung mit allen Bausteinen war nicht unterzubringen. Eine Lösung mit zwei Karten erschien indiskutabel und ist viel zu teuer. Also begannen wir die Karte zu optimieren. Dabei legten wir zuerst den DMA auf Eis. Dieser wird nämlich nur beim Festplattencontroller benutzt, wird aber nicht unbedingt benötigt. Selbst mit dieser Lösung war die Schaltung noch nicht auf einer Europakarte unterzubringen. Eine weitere Möglichkeit in einer solchen Situation ist eine höhere Integrationsdichte. Es gibt natürlich Gate-Array's, in denen die Bausteine, die für einen PC benötigt werden, alle integriert sind. Diese Gate-Array's haben allerdings bis zu 100 Pins und mehr und sind daher nicht zum Selbstbau geeignet. Außerdem sind diese Mammutchips nur

schwer zu durchschauen und widersprechen eigentlich dem einfachen modularen Konzept des NDR-Computers.

Wir haben uns deshalb darauf beschränkt, die meisten TTL-Bausteine in 5 PALs zusammen zu fassen und haben damit wieder einige Bausteine gespart. Doch damit noch nicht genug. Die Europakarte war immer noch so voll, daß wir einen weiteren Kompromiß eingehen mußten. Dieser Kompromiß fiel uns besonders schwer, da wir immer darauf geachtet haben, daß sämtliche unserer Baugruppen in der GES Norm gefertigt werden. Bei dieser Baugruppe mußten wir darauf verzichten, d.h. die Baugruppe wird nur für den NDR-Bus, nicht für den ECB-Bus geliefert werden können. Aber damit war es möglich, auf einer Karte alle nötigen Teile unterzubringen.

# Die Anpassung steckt im BIOS

Die Anpassung der gängigen NDR Standardbaugruppen, wie GDP64, FLO3 oder KEY steckt im BIOS der CPU8088. Nun kurz noch einige Anmerkungen zum BIOS allgemein. BIOS steht für "Basic Input Output System" und stellt die Schnittstelle zwischen dem Betriebssystem (hier MS-DOS) und der Hardware dar. Um das etwas näher zu erläutern, sei hier ein kleines Beispiel angeführt: Ein Anwenderprogramm verlangt, daß ein Punkt auf den Bildschirm geschrieben wird. Dabei könnte jetzt an dieser Stelle des Anwenderprogrammes direkt die Hardware angesprochen werden. Dies hätte allerdings zwei gewaltige Nachteile: Zum Ersten müssen Sie immer dieselbe Hardware verwenden, und zum Zweiten müßte der Programmierer genaue Hardwarekenntnisse haben, ganz abgesehen vom Programmieraufwand. Aus diesem Grund gibt es die BIOS (Programm-)Schnittstelle für den Befehl "Punkt auf der Graphikkarte setzten". Im BIOS steht dann an dieser Stelle die Routine, die die Graphikkarte direkt anspricht.

Für die GDP heißt dies nun, daß in unserem BIOS für die entsprechenden Befehle die Hardwaretreiber für die GDP64 stehen. Sind nun die Anwenderprogramme "sauber" geschrieben (über die BIOS Schnittstelle), so laufen die Programme, die auf einem kompatiblen PC laufen, auch auf dem NDR-Rechner mit der CPU8088 und der GDP64. Dasselbe gilt nun für die Baugruppen FLO3 und KEY, bzw. FLO2 und KEY2. Dies ist bei den meisten Programmen, die wir bisher getestet haben, auch gewährleistet. Problematisch sind allerdings die parallele und serielle Schnittstelle. Bei Einoder Ausgaben auf diese beiden Schnittstellen greifen doch mehrere Programme direkt auf die Hardware zu. Dies ist sicherlich noch eine Unsitte aus der Zeit des "Protectionismus", womit versucht wurde, Software nur auf original IBM-PCs zum Laufen zu bringen. Mittlerweile hat sich ja gezeigt, daß diese Rechnung nicht aufging, aber diese "Unsitte" ist nicht mehr auszumerzen. Aus diesem Grund haben wir diese Schnittstellen mithilfe einer Buskopplung (NDR-PC-Bus) unterstützt (billige serielle und parallele Schnittstellen für den PC Bus). Andererseits ist unsere CENT2 und unsere SER im BIOS angepaßt.

Außerdem werden wir im BIOS noch folgende Zusatzhardware unterstützen:

- SMART Watch (nach dem Booten wird die aktuelle Zeit im DOS eingetragen).

Festplätte: Hier unterstittzen wir eine Standardfestplätte (Seagate 225) mit dem OMTI-Controller 5520B

Ein Nachteil der GDP beim Betrieb mit der CPU8088 sei nicht verschwiegen: Die GDP unterstützt nicht den vollen IBM-Zeichensatz. Da wir aber kompatibel bleiben wollten, werden nun die IBM-Zeichen einzeln durch das BIOS "gezeichnet". Nur kostet das Zeit.

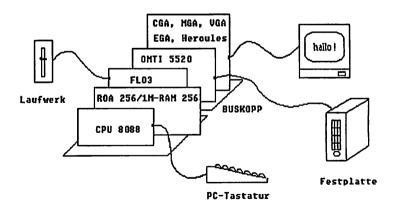

Für diejenigen, die sich mit der Geschwindigkeit der GDP nicht anfreunden können, werden wir mit der Buskopplung NDR PC-Bus auch eine Hercules, EGA, CGA oder VGA Karte unterstützen. Wer mit der KEY und der ASCII-Tastatur nicht klar kommt, oder unbedingt eine MF II Tastatur haben möchte, kann diese direkt an der CPU8088 anschließen. Diese Tastatur wird dann vom BIOS erkannt.

Hier noch einmal zusammengefaßt eine Liste der vom BIOS unterstützten PC-Baugruppen:

Graphikkarten: MGA (Monochrom Graphik Adapter)

Hercules Karte

CGA (Colour Graphik Adapter)

EGA (Enhanced Graphik Adapter)

VGA (Video Graphics Adapter)

Festplatten: OMTI 5520 (Adapter für gängige Festplattenlauf-

werke)

- Sonstige: Parallele Schnittstelle (Centronics)

Serielle Schnittstelle

Wie Sie sicher jetzt erkannt haben, gibt es zahlreiche Möglichkeiten mit dem NDR-Computer PC-kompatibel zu werden. Die einfachste ist sicher, nur die CPU zu wechseln. Aber es gibt auch Möglichkeiten, sich seinen NDR-PC bis zur Festplatte aufzurüsten und dies zu einem relativ günstigen Preis.

Wir hoffen Ihnen hier die Tragweite dieser Entwicklung etwas näher gebracht zu haben, und Ihnen auch einen Überblick über die Möglichkeiten des NDR-Rechner auf PC-Basis gegeben zu haben.

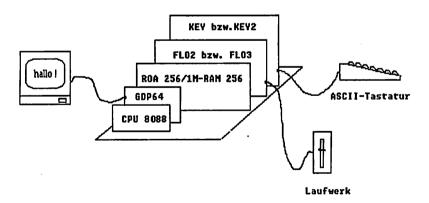

#### 1.3 Wie setzt man die CPU8088 ein

Bisher war es relativ schwierig, den NDR-Computer wirklich IBM- und damit MS-DOS kompatibel zu machen. Mit der neuen CPU8088 ist es jetzt ganz einfach, mit dem Betriebssystem MS-DOS zu arbeiten:

Die CPU, mit der bisher gearbeitet wurde, einfach herausnehmen, die Neue reinstekken und damit ist eigentlich alles Wesentliche getan. Alle Baugruppen, die vorher verwendet wurden, funktionieren noch immer und sogar mit dem alten NDR-Laufwerk ist es jetzt möglich, IBM-Format zu lesen.

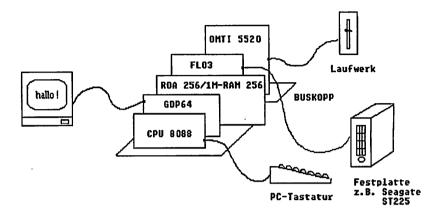

Für die Zukunft wird es weitere Möglichkeiten der Systemkonfiguration geben: Über die Buskopplung NDR-IBM wird mit Hilfe des OMTI-Controller 5520B eine Festplatte unterstützt. Ebenfalls über die Buskopplung sollen parallele und serielle PC-Schnittstellen, sowie PC-Graphikkarten unterstützt werden. Die Erkennung, welche Karten im System stecken, wird das System (BIOS) selbst durchführen. Unten sehen Sie drei Möglichkeiten der Systemkonfiguration.

Abb.: Grundkonfiguration NDR mit CPU8088

Abb.: mögliche Konfiguration NDR CPU8088

#### 2. Technische Daten

- CPU8088-1 = 8088 CPU mit 10 MHz (auch NEC V20)

- Sockel für 8087-1 vorgesehen

- 3 Timer 8253

- Interruptcontroller 8259

Taktgenerator und RESET-Baustein 8284-1 (10 MHz)

- Buscontroller 8288

- paralleler Schnittstellen-Baustein 8255

- Keyboard-Controller für PC-Tastatur

- Speaker Ausgang (8 Ohm Lautsprecher)

- WAIT-Logik

- 8K ROM (BIOS), max. 32K ROM

- 32K RAM

- BIOS unterstützt IBM monochrom Zeichensatz (Pseudographik)

- BUS: NDR-Bus

- Stromaufnahme +5V: 700mA

- Leiterplattenformat: 100 x 160

# Sämtliche Karten des NDR-Computers können verwendet werden:

GDP64k KEY mit paralleler Tastatur ROA64, RAM64/256, ROA256/1M FLO3 mit TEAC-Laufwerken (FD55F..) sämtliche I/O Karten

Benchmarks:

Nortonfaktor 3.4

Landmark Test:

CPU Speed entspricht der eines AT's bei 3,6 MHz

Landmark Faktor im Vergleich zum IBM PC (4.77 MHz): 1.8

# 3. Prinzipbeschreibung

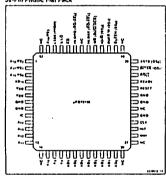

# 3.1 Blockschaltbild

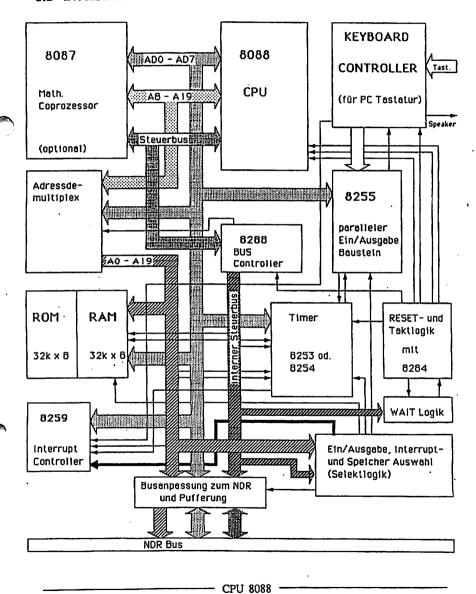

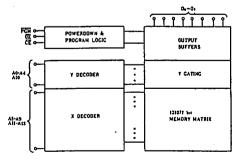

# 3.2 Beschreibung des Blockschaltbildes

Die Schaltung der CPU8088 ist relativ komplex und dementsprechend undurchsichtig. Aus diesem Grund ist ein übersichtliches Blockschaltbild unerläßlich. Selbst das Blockschaltbild ist noch relativ voll, aber es läßt sich leider nicht mehr vereinfachen, ohne dabei ins Triviale und Nichtssagende zu verfallen.

#### 3.2.1 Die CPU

Die 8088 CPU ist das Herz der Baugruppe und des Rechners. Sie kommt entweder von INTEL und ist mit 8088-1 (10 MHz) bezeichnet, oder sie kommt von NEC und trägt die Aufschrift V20-10MHz. Die CPU steuert sämtliche Vorgänge im Rechner (Verwaltung der Speicher und Ein/Ausgabe Einheiten, Ablauf von Programmen, Rechenarbeit...).

Der Prozessor 8088 ist ein 8-Bit-Prozessor mit interner 16-Bit-Architektur. Der Prozessor ist softwarekompatibel zum 8086 und kann 1 MByte direkt adressieren. Nähere Angaben zur 8088 CPU siehe unter 10.2 Datenblatt 8088 CPU.

## 3.2.2 Der Coprozessor

Der 8087 ist ein Mathematik Coprozessor, der standardmäßig nicht im Lieferumfang eines PC's enthalten ist. Deshalb haben auch wir darauf verzichtet, den 8087, der doch relativ teuer ist, standardmäßig mitzuliefern. Bei Software-Problemen mit vielen mathematischen Gleichungen bringt der 8087 allerdings einen großen Zeitgewinn, da der Prozessor mathematische Funktionen direkt berechnet (Das heißt, dem Coprozessor wird nur ein Befehl übergeben und anschließend das Ergebnis abgeholt).

#### 3.2.3 Der "Adreßdemultiplex"

Der Block Adreßdemultiplex macht vom Prinzip her nichts anderes, als die gemultiplexten Adreß- und Datenleitung AD0 bis AD7 zu trennen. Am Ausgang sind dann nur noch die Adreßleitungen A0 bis A7 und zusätzlich A8 bis A19, die außerdem noch gepuffert werden. Die Steuerung dieses "Adreßdemultiplexers" wird vom Signal ALE (Adress Latch Enable) gesteuert, das der Bus-Controller 8288 erzeugt.

#### 3.2.4 Der Bus-Controller

Der BUS-Controller 8288 erzeugt aus den Prozessorsignalen S0, S1 und S2, die für den PC-Bus benötigten Signale:

| -IOR  | (Ein/Ausgabe lesen)                     |

|-------|-----------------------------------------|

| -IOW  | (Ein/Ausgabe schreiben)                 |

| -MEMR |                                         |

| -MEMW | (Speicher schreiben)                    |

| -DT/R | (Daten senden oder empfangen)           |

| -DEN  | (Daten Freigabe)                        |

| -ALE  | (Adreßfreigabe und Zwischenspeicherung) |

| -INTA | (Quittieren eines Interrupts)           |

Diese Signale werden zum Ablauf von Speicher- und Ein/Ausgabe-Zugriffen, sowie zur Interruptabwicklung benötigt.

# 3.2.5 Die Speicher

An Speichern befinden sich auf der Baugruppe maximal 64KB, die sich in 32K ROM und 32 K RAM aufsplitten. Der ROM-Bereich wird in der Regel für das BIOS genutzt. Wer die Karte aber als Single Board Computer für irgendwelche Steuerungen verwenden will, kann hier natürlich auch sein eigenes EPROM stecken. Der RAM Bereich (statisches RAM 32K \* 8), dient als "Shadow RAM". Dieser Speicher simuliert eine Graphikkarte, die normalerweise bei einem PC auf diesem Speicherbereich liegt. Dadurch ist es möglich, im Hintergrund (Schattenspeicher) die Graphik aufzubauen und durch Vergleich mit dem GDP Speicher auf der GDP64 zu aktualisieren.

#### 3.2.6 Der Interrupt-Controller

Der Interrupt-Controller 8259 ist für die Abwicklung der Interrupts verantwortlich. Dieser Baustein stellt 8 Interrupt-Eingänge zur Verfügung. In unserer Schaltung sind nur 5 belegt:

Zeitgeber Tastatur Parallel-Drucker 2 Asynchron-Adapter

Wird nun ein Interrupt von einem dieser Geräte ausgelöst, so gelangt dieser zum 8259, der dann den Prozessorinterrupt aktiviert und auf das Quittierungssignal (INTA) wartet. Ist dieses aktiv, so wird der Interrupt-Vektor eingelesen und in die Interrupt-Routine verzweigt. Außerdem bietet der Baustein noch einige Extras, wie Prioritätsbehandlung, Kaskadierbarkeit ...

#### 3.2.7 Timer

Der Baustein 8253 oder 8254 (schnelle Version) beinhaltet 3 Timer, wobei bei unserer Schaltung nur zwei verwendet werden. Der erste Timer wird ausschließlich für die Systemuhr benutzt. Dabei wird ein Takt von 1,19 MHz angelegt und der Timer macht dann nichts anderes, als die Taktzyklen zu zählen und in bestimmten Zeitabständen einen Interrupt zu senden. Dabei wird dann bei jedem 18. Interrupt der Sekundenzähler um Eins erhöht. Der zweite Timer wird zur Synchronisation der seriellen Tastaturdaten verwendet.

# 3.2.8 Die RESET- und Taktlogik

Die RESET- und Taktlogik erzeugt zunächst einmal den Systemtakt für den Prozessor 8088 und den Coprozessor 8087. Dabei wird die Quarzfrequenz von 28,62 MHz durch drei geteilt, also 9,54 MHz. Außerdem wird über diesen Baustein auch der Takt für den Timer erzeugt. Dabei wird die Quarzfrequenz vom 8284 erst durch drei, dann durch zwei und anschließend mit zwei Flip-Flops noch zweimal durch zwei geteilt. Dadurch erhält man den Timertakt von 1,1925 MHz, der für die Systemuhr verwendet wird.

Zum Zweiten erzeugt dieser Baustein ein RESET-Signal aus einem analog erzeugten RESET (RC-Glied für Power on RESET und RESET-Taster). Dieses analog ansteigende Signal wird an den Eingang -RES (mit Schnitt-Trigger) angelegt und auf dem Ausgang RESET mit einer bestimmten Periodendauer an den Prozessor weitergeleitet.

Zum Dritten enthält der Baustein eine Logik zum Synchronisieren des READY-Signals. Dabei können zwei READY-Signale von außen angelegt werden, die dann mit dem Systemclock synchronisiert an den Prozessor weitergeleitet werden. Hier wird nur ein READY-Signal verwendet. Dieses READY-Signal wird von der WAIT-Logik erzeugt.

## 3.2.9 Die WAIT-Logik

Damit wären wir bereits bei der WAIT-Logik angelangt. Der Ausdruck WAIT hat bei den Computer-Anwendern einen negativen Beigeschmack, weil damit immer eine Verlangsamung des Rechners gemeint ist. Aus systemspezifischen Gründen sind aber WAITs bei bestimmten Zugriffen unerläßlich, um schnelle teure Bausteine zu sparen. Natürlich versucht man, WAITs nur dort einzubauen, wo sie am wenigsten Zeit kosten. Dies ist bei den Ein/Ausgaben der Fall, da auf diese Einheiten im Vergleich zu Speichern nur sehr selten zugegriffen wird. WAIT-States werden in unserer Schaltung bei Zugriffen auf den Timer, auf den Interrupt-Baustein und auf den parallelen Ein/Ausgabe-Baustein eingefügt. Außerdem natürlich auch, wenn vom NDR-Bus ein WAIT-Signal anliegt.

#### 3.2.10 Die Ein/Ausgabe

Der parallele Ein/Ausgabe-Baustein 8255 dient nur zum Einlesen der Tastatur, zur Steuerung des Ablaufs des Keyboard-Controllers, sowie zur Datenausgabe an den Lautsprecher.

#### 3.2.11 Der Keyboard-Controller

Der KEYBOARD-Controller auf der CPU8088 ist so ausgelegt, daß eine PC-Tastatur (auch MF-II Tastaturen, die auf PC- oder XT-Modus umschaltbar sind) angeschlossen werden kann. Dabei muß diese PC-Tastatur aber nicht verwendet werden, denn es funktioniert auch die KEY und daran die Tastaturen TAST1, TAST2 und TAST3. Das BIOS erkennt selbst welche Tastatur vorhanden ist. Die PC-Tastatur hat die höhere

Priorität, d.h. steckt die KEY aus Versehen im Rechner und ist eine PC-Tastatur an der CPU8088 angeschlossen, so wird die PC-Tastatur erkannt und verwendet. Eine PC-Tastatur bietet natürlich mehr Bedienungskomfort. Vor allem die Darstellung der Sonderzeichen und das Betätigen der Funktionstasten verlangt bei den bisherigen NDR-Tastaturen doch einige Klimmzüge, aber es können mit TAST1, TAST2 und TAST3 alle möglichen Zeichen dargestellt werden.

Nun zurück zum KEYBOARD-Controller: Dieser macht nichts Anderes, als die seriell ankommenden Zeichen in ein paralleles Format umzuwandeln. Diese parallelen Zeichen werden dann an den 8255 weitergegeben und eingelesen. Der Ablauf beim Einlesen eines Zeichens wird über Interrupt gesteuert. Das heißt, kommt ein Zeichen von der Tastatur, wird ein Interrupt ausgelöst, das Zeichen eingelesen und in einem Puffer abgelegt (Softwarepuffer). Sollte keine PC-Tastatur angeschlossen sein, sondern eine NDR-Tastatur, so verfügt auch diese über den Softwarepuffer. TAST1, TAST2 und TAST3 haben also bei Betrieb mit MS-DOS einen Zeichenpuffer (Größe des Zeichenpuffers im DOS definiert).

## 3.2.12 Die Select-Logik

Die Select-Logik wählt, wie der Name schon sagt, die einzelnen Speicher oder Ein/Ausgabe-Bausteine aus. Das heißt, liegt z.B. der ROM-Speicher von Adresse 0 bis 7FFFh, so wird, wenn eine Adresse in diesem Adreßraum angesprochen wird, dieser Baustein aktiviert (Chip-Select-Signal). Ebenso verhält es sich bei den Portadressen von Ein/Ausgabe Bausteinen. Diese Chip-Select Signale werden von der Select-Logik erzeugt.

#### 3.2.13 Die Busanpassung

Die Busanpassung zum NDR-Bus besteht im wesentlichen aus zwei Bausteinen. Zum Einen werden die Signale

-IOR, -IOW, -MEMR, -MEMW

auf die NDR-Bussignale

-RD, -WR, -IORQ, -MREQ

umgelegt und das RESET-Signal invertiert, zum Andern werden die Daten über einen bidirektionalen Bustreiber gepuffert und bei Zugriff auf externe Baugruppen (Speicher, Ein/Ausgabe) freigegeben.

Die Beschreibung des Blockschaltbildes wurde absichtlich etwas ausführlicher gehalten, um die einzelnen Blöcke etwas zu durchleuchten. Wollen Sie noch tiefer einsteigen, können Sie in der Schaltungsbeschreibung unter Kapitel 7 und in den Datenblätter unter Kapitel 10 Detailinformationen nachlesen.

# 4. Aufbauanleitung

# 4.1 CMOS-Warnung

CMOS-Bausteine sind hochempfindlich gegen elektrostatische Aufladung! Bewahren oder transportieren Sie CMOS-Bausteine nur auf dem leitenden Schaumstoff! Alle Pins müssen kurzgeschlossen sein.

Tip: Fassen Sie an ein geerdetes Teil (z.B. Heizung, Wasserleitung), bevor Sie einen Baustein berühren.

Bitte beachten Sie hierzu auch den Artikel "Schutzmaßnahmen für MOS-Schaltungen" in unserer Zeitschrift LOOP3.

# 4.2 Stückliste

| 1  | 11267 | CPU8088H | CPU8088-Handbuch                                 |

|----|-------|----------|--------------------------------------------------|

| 1  | 61256 | CPU8088P | CPU8088-Leiterplatte mit Lötstoplack und         |

|    |       |          | Bestückungsdruck                                 |

| 2  | 60183 | SO14     | IC Sockel 14 polig                               |

| 1  | 60186 | SO18     | IC Sockel 18 polig                               |

| 11 | 60187 | SO20     | IC Sockel 20 polig                               |

| 3  | 60190 | SO28     | IC Sockel 28 polig                               |

| i  | 60188 | SO24     | IC Sockel 24 polig                               |

| 3  | 60193 | SO40     | IC Sockel 40 polig                               |

| 2  | 69167 | 74LS74   | J9,10 D-Flip Flop mit Preset                     |

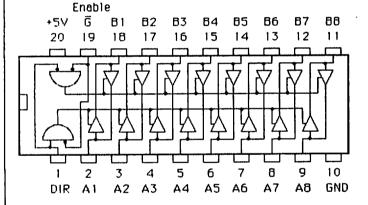

| 1  | 60115 | 74LS245  | J14 8-Bit Bus-Transceiver                        |

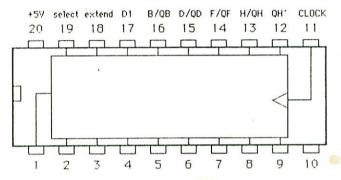

| i  | 61243 | 74LS322  | J5 8-Bit Schiebereg, mit 'sign extend'           |

| 3  | 60125 | 74LS373  | J15,17, 8-Bit D Register mit Tri-State Ausgängen |

| ,  | 00123 | 7120515  | J18                                              |

| 1  | 61242 | 8253     | J3 Timerbaustein                                 |

| i  | 61241 | 8255     | J4 PIO                                           |

| i  | 61240 | 8259     | J8 Interrupt-Controller                          |

| i  | 61239 | 8284-1   | J12 Clock Generator                              |

| i  | 61238 | 8288     | J13 Buscontroller 8MHz                           |

| 1  | 61257 | 2764     | J6 BIOS-EPROM                                    |

| 1  | 11068 | 82256    | J7 RAM 32KB, 120ns, stat.                        |

| 1  | 61237 | NEC V20  | J2 CPU 8088-kompatibel                           |

| 1  | 61269 | PAL16L8  | J19 PAL1                                         |

| ı  | 01409 | しいかしのいり  | JIZ IAGI                                         |

| 1  | 61256 | PAL         | 16L8      | J16  | PAL2                                     |

|----|-------|-------------|-----------|------|------------------------------------------|

| 1  | 61270 | PAL         | 16L8      | J21  | PAL3                                     |

| 1  | 61271 | GAL         | 16L8      | J11  | PAL4                                     |

| 1  | 61272 | PAL         | 16R4      | J20  | PAL5                                     |

| 1  | 61247 | XTA         | L         | Q1   | Quarz 28.62 MHz                          |

| 1  | 60290 | 1N41        | 48        | D1   | Silizium-Diode                           |

| 1  |       | BC10        | )7        | T1   | NPN-Transistor                           |

| 3  | 60758 | RN4         | *4K7      | RN13 | Netzwerkwid, 4x4.7 kOhm                  |

| 5  | 60648 | R           | R7 - R10, | R12  | Widerstand 4.7 kOhm (gelb, violett, rot) |

| 1  | 60617 | R           | R1        |      | Widerstand 10 kOhm                       |

| •  | 0001. | ••          |           |      | (braun, schwarz, orange)                 |

| i  | 60626 | R           | R5        |      | Widerstand 1 kOhm                        |

| -  |       |             |           |      | (braun, schwarz, rot)                    |

| 2  | 61248 | R           | R2,3      |      | Widerstand 510 Ohm                       |

|    |       |             |           |      | (grün, braun, braun)                     |

| 1  | 60642 | R           | R4        |      | Widerstand 33 Ohm                        |

|    |       |             |           |      | (orange, orange, schwarz)                |

| 2  | 60635 | R           | R6,11     |      | Widerstand 27 Ohm                        |

|    |       |             |           |      | (rot, violett, schwarz)                  |

| 2  | 60248 | C 10        | •         |      | Tantalelko 10uF/16V                      |

| 19 | 60239 | <b>C</b> 10 | •         |      | Keramikkond, 100nF                       |

| 1  | 60301 | Taste       |           | S1   | Resettaster                              |

| 1  | 61255 | Stec        |           | BU1  | Tastaturanschl. DIN41524                 |

| 2  | 60493 |             | e JMP3,   | ST1  | Stiftleiste 2 x 1 pol. gerade            |

| 1  | 60502 |             | e JMP1,   | ST   | Stiftleiste 4 x 2 pol. gerade            |

| 1  | 10405 |             | ST2       | ST2  | Stiftleiste 18 x 1 pol. gew.             |

| 1  | 10406 | Stift       | e ST2     | ST2  | Stiftleiste 36 x 1 pol. gew.             |

| 2  | 60486 | Jump        | per       |      | Shuntstecker                             |

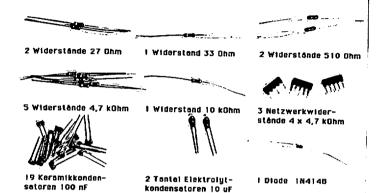

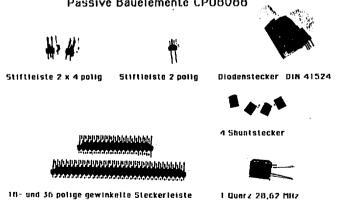

# Passive Bauelemente CPU8088

# Passive Bauelemente CPU8088

Abb.6: Bauteile CPU8088

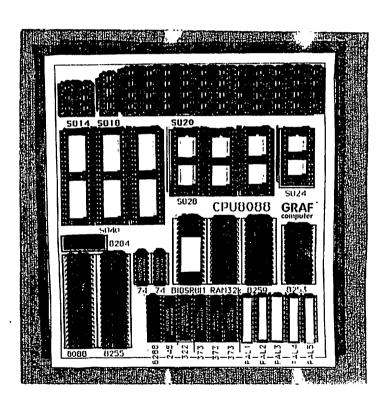

Abb.: ICs und Sockel

- CPU 8088 ·

#### 4.3 Aufbau Schritt für Schritt

Benötigtes Werkzeug:

Lötkolben mit temperaturgeregelter Spitze Lötzinn, säuerefrei, mit Kolophonium-Seele Pinzette Elektroniker-Seitenschneider

Die Leiterplatte ist sehr eng bestückt. Bitte bauen Sie nur dann selber auf, wenn Sie über ausreichend Erfahrung im Aufbau von eng bestückten Leiterplatten verfügen.

Die Lötseite erkennt man an der Aufschrift "Lötseite". Ausschließlich auf dieser Seite der Leiterplatte wird gelötet. Die Bauteile werden nur auf der Bestückungsseite bestückt.

Beim Aufbauen der Baugruppe arbeiten Sie sich am günstigsten etappenweise voran, das soll heißen: alle Teile einer Bauteilgruppe werden auf einmal bestückt. Die Anschlußdrähte der Bauteile werden durch die entsprechenden Lötaugen geschoben, bis der Bauteilkörper flach auf der Platinenoberseite aufliegt. Die Anschlußdrähte werden, wenn möglich, auf der Lötseite leicht abgewinkelt, damit das betreffende Bauteil eine erste Fixierung erhält. Nachdem Sie sicher sind, daß keine Fehlbestückung (falsche Bauteile, Position oder Lage) vorliegt, werden alle bisherigen Anschlüsse verlötet und danach, wenn notwendig, zu weit überstehende Anschlußdrähte gekürzt.

Eine etwas andere Vorgehensweise empfiehlt sich bei den IC-Sockeln: Sie werden zuerst alle, von der Bauteileseite her, eingesetzt und danach mit einem Stück Karton abgedeckt, damit sie beim Umdrehen der Bauguppe in ihrer Position gehalten werden. Bevor nun endgültig alle Anschlußbeine verlötet werden, sollten erst einmal zwei Beinchen pro Sockel gelötet werden (diagonal versetzt). Ungleichmäßigkeiten im Abstand vom Sockel zur Platinenoberfläche und - ganz wichtig - eine eventuell falsche Lage einzelner Sockel (Kerbe in der Fassung muß in die selbe Richtung weisen, wie die 'Nase' auf dem Bestückungsdruck) können zu diesem Zeitpunkt noch korrigiert werden. Das vorläufige Anheften empfiehlt sich übrigens bei

allen Bauteilen mit mehr als zwei Anschlußdrähten (Transistoren, Stiftleisten etc.)!

# Nach den vielen Ratschlägen, frisch ans Werk:

Beginnen Sie mit dem Einlöten der liegenden Einzelwiderstände (R1...R12) und der Diode D1.. Die Widerstandswerte können anhand der aufgedruckten Farbringe abgelesen werden. Die Bedeutung der Farben, bzw. die erforderliche Farbenfolge ist für jeden Widerstandswert in der Stückliste angegeben. Achtung: Der Widerstand R6 ist auf dem Bestückungsdruck CPU8088 r2 falsch bezeichnet. Hier darf kein 4,7 kOhm

Widerstand eingelötet werden, sondern ein 27 Ohm Widerstand. Beim Einsetzen der Diode ist auf die richige Polung zu achten! Ein Strich rund um die Diode markiert die Kathode. Auf dem Bestückungsdruck ist die Kathode mit dem Strich auf der Pfeilspitze gekennzeichnet.

Nun folgt die Bestückung der IC-Sockel, wie oben beschrieben. Die Orientierung der Fassungen ist auf der Bestückungsseite der Leiterplatte durch den Aufdruck sehr deutlich zu erkennen: Die eingezeichnete 'Nase' muß sich mit der am Sockel eingearbeiteten Kerbe (falls vorhanden) decken. Achten Sie bitte darauf, daß Sie nicht einen 14-poligen Sockel auf den Platz eines 16- oder 18-poligen setzen.

Beim anschließenden Einlöten der 54-poligen (18 + 36) NDR-Bus-Steckerleiste ST2, der Jumper 1...3 sowie des Steckers ST1 müssen Sie, wie oben angedeutet, darauf achten, daß die Isolierkörper parallel zur Leiterplatte liegen. Jumper 1 und 2 sind doppelreihige Stiftleisten, Jumper 3 ist einreihig.

Bei den Tantalkondensatoren C2, C21, muß auf deren Polung geachtet werden: Der Pluspol ist auf der Platine und auf dem Kondensator entsprechend gekennzeichnet (siehe auch Skizze 1). Die Keramikkondensatoren C1,C3..C20 sind ungepolt und können, ohne auf die Polung zu achten, eingelötet werden.

Die Netzwerkwiderstände RN1...RN3 haben jeweils einen Anschluß für den Pluspol, der auf dem Netzwerkwiderstand und auf der Leiterplatte mit einem (kleinen) Punkt gekennzeichnet ist. Es handelt sich um 4 \* 4,7 kOhm Netzwerkwiderstände u.a. mit dem Aufdruck: 472 (= 47 \* 10 ² Ohm).

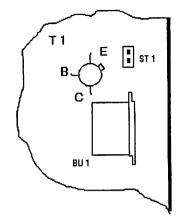

Die Anschlüsse des Transistors T1 sind ebenfalls auf der Platine, bzw im Bestückungsplan, gekennzeichnet (siehe Skizze 2). Betrachtet man den Transistor (Metall-Gehäuse TO18), so ist der Emitter dasjenige Beinchen, das der Lasche am Gehäuserand am nächsten ist. Bei Transistortypen mit Kunststoffgehäuse liegt der Emitter in der Regel bei der rechten Körperkante (wenn der Transitor in Normallage stehend betrachtet wird).

Abschließend werden noch der Resettaster S1, der Tastaturanschlußstecker BU1 und der Quarz Q1 eingelötet.

Bevor Sie jetzt schon ungeduldig die IC's einstecken wollen, sollten Sie mit Kapitel 5.1 weiter weitermachen!

Skizze 1: Polung C2

Skizze 2: Polung Transistor

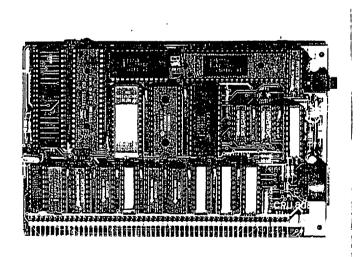

Abb.: Foto Fertiggerät CPU 8088

- CPU 8088 -

# 5. Testanleitung

# 5.1 Erste Prüfung ohne IC 's

Dieser Test wird auf der, mit den Sockeln und den passiven Bauelementen bestückten, Leiterplatte durchgeführt (Der Transistor Q1 und die Diode können natürlich auch schon eingelötet sein).

Überprüfen Sie zunächst mit einem Ohmmeter den Widerstand zwischen den Versorgungsleitungen: +5V (ST2/Pins 4,5) und Masse (ST2/Pins 6, 7, 52, 53). Hier darf der gemessene Wert keinesfalls niederohmig sein! Werte größer als 10kOhm sind normal. Wenn Sie einen abweichenden Wert feststellen, fahren Sie bitte mit Kapitel 6 fort (Fehler suchen)!

Wenn Sie die Möglichkeit haben, Ihr System auch ohne die neue CPU8088 zu betreiben (Z80- oder 680xx-System), stecken Sie die bis jetzt halbfertige Baugruppe CPU8088 erst einmal dort dazu. Nach dem Einschalten des Systems muß der Rechner auch weiterhin problemlos funktionieren (Test der Daten- und Adressleitungen auf Kurzschluß). Falls nein - weiter mit Kapitel 6.

Haben Sie diese Möglichkeit nicht, können Sie als vorsichtiger Mensch die BUS-Kontakte an ST2 mit dem Ohmmeter überprüfen (Jeder gegen Jeden). Auch hier müssen hochohmige Werte zu messen sein. Anschließend wird die Baugruppe auf den BUS gesteckt (wenn sie nicht bereits in einem anderen System steckt) und die Spannungsversorgung an den BUS gelegt.

Alle IC-Sockel werden auf die Versorgungsspannung von +5V geprüft. Bei Standard-TTL-Bausteinen, den fünf PALs und den Speicherbausteinen J6 und J7 liegt die Versorgungsspannung jeweils auf dem letzten Pin einer Fassung (z.B. bei 14-poligen Fassungen an Pin 14; bei 20-poligen Fassungen an Pin 20) an. Die Masse liegt jeweils auf dem letzten Pin der ersten Reihe (bei 14-poligen Fassungen Pin 7; bei 20-poligen Fassungen an Pin 10). Auch bei den INTEL-Bausteinen 8088 (bzw. V20, J2), 8087 (J1), 8253 (J3), 8288 (J13), 8284 (J12) und 8259 (J8) herrschen die gleichen Verhältnisse vor. Lediglich der INTEL-PIO 8255 (J4) macht hier eine Ausnahme: +5V liegt an Pin 26 und Masse (GND) liegt an Pin 7. Sind die Versorgungsspannungen an den richtigen Pins gemessen worden, können die IC's eingesetzt werden. Schalten Sie dazu den Rechner aus und ziehen Sie die Baugruppe heraus. Beim Einsetzen muß auf die Richtung der IC's geachtet werden. Die Markierung auf dem IC muß mit der Kerbe in der Fassung übereinstimmen (vgl. Bestückungsplan).

Prüfen Sie noch einmal die Lötseite der Baugruppe auf eventuelle Lötbrücken! Zur Stellung der Jumper 1...3, siehe Kapitel 5.4.

# 5.2 Test im System

# 5.2.1 Startkonfiguration

Um der CPU8088 erste Lebenszeichen zu entlocken, ist folgende Mindestkonfiguration erforderlich:

BUS2, GDP64xx + Monitor, PC-Tastatur oder 'NDR-Tastatur' + KEY, RAM-Speicher (ROA64), Netzteil mit 5V/2A (POW5V).

#### 5.2.2 Zum ersten Mal Einschalten

Wenn Sie eine PC-Tastatur einsetzen wollen, wird diese direkt an der CPU8088-Baugruppe (BU1) eingesteckt, ansonsten ist die NDR-übliche Kombination (Tastatur + KEY-Baugruppe) zu verwenden. Der RAM-Speicher muß ab Adresse 00000h zu adressieren sein (Jumper auf der ROA64, ROA256 oder RAM256 entsprechend gesteckt). Nachdem die Spannungsversorgung eingeschaltet wurde, sollte sich am betriebsbereiten Monitor eine BIOS-Copyrightmeldung zeigen. Wenn an ST1 der CPU8088 ein (Miniatur-) Lautsprecher angeschlossen ist, ist außerdem ein kurzer 'Piepser' zu hören. Gibt der Lautsprecher keinen Ton von sich oder "piepst" er zweimal, liegt im ersten Fall ein Hardwarefehler auf der CPU vor oder im zweiten Fall ein Konfigurationsfehler vor.

# 5.2.3 Vorbereitungen für MS-DOS

Um nun von einer MS-DOS Systemdiskette (V3.3) zu booten, sind weitere Voraussetzungen bezüglich der Systemkonfiguration zu erfüllen:

Das System muß um eine FLO2, bzw. FLO3 und um ein TEAC-Laufwerk 'NDR-Standard' ergänzt werden (Interrupt auf der FLO2 bzw. FLO3 Baugruppe geöffnet).

#### Achtung!

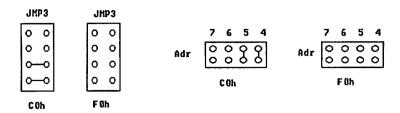

Setzen Sie die EGA- Karte mit der unter 1.2 angesprochenen Buskopplung ein, so müssen Sie die Standardadressen der FLO3 (auch FLO2) ändern: von bisher C0h auf F0h.

Abb.: Porteinstellung FLO3 Abb.: Porteinstellung FLO2

Damit einhergehend ist auch ein Netzteil mit zusätzlich \*/-12V/2A (z.B.: NE3) erforderlich. Der System-RAM-Speicher muß auf mindestens 256KB aufgestockt werden. Der 'NDR-PC' ist jetzt in der Lage von 5 1/4"-Disketten im IBM-Standardformat (360KB) das Betriebsystem MS-DOS zu booten. Nachdem Sie sich in der MS-DOS-Umgebung befinden, können Sie noch die Arbeitsweise der System-Softwareuhr überprüfen, indem Sie gewisse Zeit nach dem Booten die momentane Uhrzeit mit: TIME<Return> abfragen. Wenn dieser Test die Uhrzeit aktuell anzeigt, ist gewährleistet, daß die wesentlichen Funktionen der CPU8088 erfüllt sind (Timer- und Interruptfunktionen).

# 5.4. Jumpereinstellungen

Mit nur drei einzustellenden Jumpern ist hier relativ wenig zu tun, jedoch ist keiner voreingestellt, wie es bisher üblich gewesen ist.

#### JMP1:

Hiermit wird die Größe des eingesetzten BIOS-EPROMs eingestellt (vorläufig reichen noch 8K-EPROMs '2764' für das BIOS).

JMP1

o-o

o

o

für 8K-EPROM 2764 (Standardeinstellung)

o

o

JMP1

o

o

für 32K-EPROM 27256

o-o

#### JMP2:

Damit kann die Taktrate für den Timerbaustein (und damit auch für die Softwareuhr) umgeschaltet werden. Normalerweise (mit der 10 MHz-Standardbestückung) muß JMP2 wie folgt gesteckt sein, damit sich eine 'Triggerfrequenz' von ca. 18Hz ergibt:

#### JMP2

o o für Standardbestückung mit

o--o Quarz 28,62MHz

Alternativ kann aber auch ein Quarz mit der Frequenz von 14,31 MHz eingesetzt werden, um einen CPU-Takt von 4,77 MHz zu erhalten (Kompatibilität zu bestimmten Programmen, preiswertere Bausteine). Damit aber die Systemuhr trotzdem nicht um die Hälfte zu langsam geht, kann mit JMP2 eine Timertakthalbierung umgangen werden, indem er so umgesteckt wird:

#### JMP2

o--o für alternative Bestückung mit Quarz 14,31MHz

0 0

#### JMP3:

Wenn Sie einen mathmatischen CO-Prozessor (8087-1) einsetzen, muß JMP3 gebrückt werden, ansonsten bleibt er offen.

# 6. Anweisungen zur Fehlersuche

Zuallererst:

Entfernen Sie die Flußmittelrückstände auf der Lötseite der Baugruppe. Am besten mit Spiritus und einer kleinen, weichen Bürste. Beachten Sie aber die Hinweise auf der Spiritusflasche zum Schutz Ihrer Gesundheit und der Ihrer Mitmenschen!

Wir wollen Ihnen hier Vorschläge machen, wie eine systematische Fehlersuche mit und ohne Oszilloskop vor sich gehen kann:

1. Altes System: Sind die bisher verwendeten Baugruppen in Ordnung? (Falls Sie noch eine andere CPU haben: Funktionierte das System

ohne die CPU8088?)

2. Jumper: Kontrollieren Sie noch einmal die Stellung der Jumper nach.

3. Sichtprüfung: Können Sie bei einer Sichtprobe unsaubere Lötstellen entdek-

ken? Solche unsauberen Lötstellen, zuviel Zinn oder sogenannte 'Fäden', können Kurzschlüsse verursachen. Löten Sie solche Stellen noch einmal nach und entsernen Sie alles überflüssige

Zinn.

4. ICs: Überprüfen Sie noch einmal, ob alle ICs an der richtigen Stelle

in der richtigen Richtung stecken. Am besten vergleichen Sie

deren Lage nochmal mit dem Bestückungsplan.

5. Gepolte Bauteile: Überprüfen Sie die Lage der gepolten Bauteile (Elkos, Dio-

den, usw.).

6. Lötstellen: Schauen Sie sich Ihre Platine noch einmal genau an: Können

Sie irgendwo 'kalte' Lötstellen entdecken? Kalte Lötstellen erkennt man daran, daß sie nicht glänzen, sondern matt und trüb sind. Oder entdecken Sie etwa vergessene, gar nicht gelötete Stellen? Im Zweifelsfall alle 'verdächtigen' Stellen nochmal

nachlöten.

7. Zu heiß gelötet? Wenn der Lötkolben zu heiß eingestellt war, oder wenn Sie

beim Löten zu lange auf dem Lötauge geblieben sind, kann es passieren, daß sich das Lötauge oder Leiterbahnen von der Leiterplatte gelöst haben und Unterbrechungen bilden. Eventuell wurden auch Durchkontaktierungen oder sogar einzelne Bau-

teile zerstört.

| CP | I | ጸበ | 21 |

|----|---|----|----|

|    |   |    |    |

Beheben Sie solche Fehler, wenn Sie sie finden, mit einem kleinen Drahtstück, um die Unterbrechung zu überbrücken. Bauteilefehler, besonders defekte ICs, sind ohne Meßwerkzeuge wie Oszilloskop oder Logikanalysator nur schwierig festzustellen.

#### 8. Leiterbahnen

Prüfen Sie mit einem Durchgangsprüfer anhand des Layouts alle Leiterbahnen auf Durchgang. Sie tun sich leichter, wenn Sie vorher alle ICs aus ihren Fassungen nehmen. Der Übersicht wegen empfiehlt es sich, überprüfte Leiterbahnen mit Bleistift oder mit Farbstift zu markieren.

# 9.Versorgungsspannung

Messen Sie mit einem Digitalvoltmeter am Bus die Versorgungsspannung nach. Toleranzen von \*/- 5% sind erlaubt.

Haben Sie alles überprüft und nichts gefunden, so ist vermutlich ein Bauteil defekt. Wenn Sie einen Prüfstift oder ein Oszilloskop haben, dann können Sie jetzt nachsehen, ob an den Ausgängen jeweils die entsprechend richtigen Signale anliegen. Welche Signale wo anliegen müssen, können Sie der Schaltungsbeschreibung, dem Schaltplan und Ihren eigenen Überlegungen entnehmen.

Ohne Messgeräte müssen Sie alle Bauteile systematisch austauschen, bis Sie das fehlerhafte Bauteil gefunden haben. Verwenden Sie dazu eventuell eine zweite Baugruppe, beispielsweise die eines Freundes oder eines Bekannten.

Sollten Sie überhaupt nicht zurande kommen, hilft Ihnen unser Pauschal-Reparatur-Service, dessen Bedingungen Sie der Preisliste entnehmen können.

# 7. Schaltungsbeschreibung

Die Schaltung der CPU8088 kann in 13 Blöcke zerlegt werden, wie Sie im Blockschaltbild (Kapitel 3) bereits erkennen konnten. Diese Aufsplittung in Blöcke ist nötig, um die Funktion der Schaltung allgemein begreifbar zu machen. Ausgehend von diesen Blöcken wollen wir hier versuchen, den Stromlaufplan dieser komplexen Schaltung zu erklären. Wir müssen hier allerdings voraussetzen, daß Sie die Beschreibung des Blockschaltbildes gelesen und verstanden haben.

#### 7.1 Der Prozessor

Der Prozessor 8088 von Intel (auch V20 von NEC) ist ein 8-Bit-Mikroprozessor, der der 8080- und 8085-Familie entspringt, aber zu diesen nicht aufwärtskompatibel ist. Dieser Prozessor steckte in dem ersten IBM-Mikrocomputer, dem legendären PC, den schließlich alle Welt nachzubauen versuchte. Mittlerweile wird dieser 8 Bit Mikroprozessor aber mit 10 MHz betrieben, und ist dann doch um einiges schneller als der damalige IBM-PC. Aber zurück zum Prozessor. Die Datenleitungen und Adreßleitungen 0 bis 7 sind gemultiplext und werden auf jeweils einem Pin herausgeführt. Ob nun Daten oder Adressen an diesen Eingängen anliegen, wird durch das Signal ALE gesteuert, das wiederum vom BUS-Controller 8288 erzeugt wird. Das Timing Diagramm hierzu kann im Datenblatt zum 8288 unter Kapitel 10 nachgeschlagen werden. Die Adreßleitung A8 bis A19 sind nicht gemultiplext. Mit den 20 Adreßleitungen kann der 8088 1 MByte direkt adressieren.

# 7.2 Die Statussignale

Die Statusleitungen -S0 bis -S2 zeigen an, was der Prozessor im Moment macht. Die Statussignale werden ebenfalls vom 8288 decodiert.

Tabelle 1: Wahrheitstabelle der Statussignale -S0, -S1 und -S2:

| -S0 | -S1 | -S2 | auszuführende Operation      |

|-----|-----|-----|------------------------------|

| 0   | 0   | 0   | Interrupt Quittierung        |

| 0   | 0   | 1   | Ein/Ausgabe-Lese-Zyklus      |

| 0   | 1   | 0   | Ein/Ausgabe-Schreib-Zyklus   |

| 0   | 1   | 1   | Halt                         |

| 1 1 | 0   | 0   | OP-Code Speicher-Lese-Zyklus |

| l 1 | 0   | 1   | Speicher-Lese-Zyklus         |

| 1 1 | 1   | 0   | Speicher-Schreib-Zyklus      |

| 1   | 1   | 1   | Passiver Zustand             |

Vom 8288 werden aber nur die Ein/Ausgabe- und Speicher-, Lese- und Schreibzugriffe decodiert, sowie das Interrupt-Quittierungssignal. Die beiden Statussignale OP-Code Speicher-Lese-Zyklus und Speicher-Lese-Zyklus werden zusammengefaßt zum Speicher-Lese-Signal (J13/7).

Die beiden Statussignale QS1 und QS0 steuern die Abarbeitung von Stapelbefehlen. Diese beiden Signale führen lediglich zum math. Coprozessor 8087-1. Nähere Einzelheiten siehe unter Kapitel 10.

Die Eingänge CLK, READY und RESET werden vom 8284 gesteuert. Auf den CLK Eingang wird ein Takt von 28,62 MHz gelegt, der durch drei (=9,54 MHz) geteilt wird, was dem Arbeitstakt der CPU entspricht. Das READY-Signal ist nichts Anderes, als das invertierte WAIT Signal, das bei Zugriffen auf Speicher oder Ein/Ausgaben erzeugt wird, und vom 8284 synchronisiert wird.

Der Befehlsatz des 8088 ist dem des 8085 sehr ähnlich. Es würde den Rahmen dieser Beschreibung sprengen, wenn wir hier näher darauf eingehen würden. Im Datenblatt unter Kapitel 10 ist eine Kurzbeschreibung der möglichen Befehle zu finden.

# 7.3 Der Coprozessor

Der 8087 ist ein mathematischer Coprozessor, der direkt mit dem 8088 verbunden wird. Ist der Coprozessor eingesteckt, verhalten sich diese beiden wie ein einziger Prozessor, das heißt, es kommen die math. Befehle hinzu, die aber so ausgeführt werden, als ob sie im Prozessor selbst ausgeführt würden. Dadurch ergeben sich natürlich große Zeitgewinne, wenn häufig mathematische Operationen verwendet werden. Allerdings muß die Software natürlich die Coprozessor-Befehle unterstützen.

# 7.4 Die Reset- und Taktlogik

Kehren wir noch einmal kurz zum Takt- und RESET-Baustein 8284 zurück. Unter Kapitel 10 ist das Schaltbild dieses Bausteines aufgeführt. Er enthält einen internen Oszillator, der nur noch durch einen externen Quarz stabilisiert werden muß. Dieser Quarz hat bei uns eine Frequenz von 28,62 MHz und liegt an J1/16/17. Es kann allerdings auch ein externer Oszillator angeschlossen werden (am Eingang J12/14).

Über den Eingang F/-C wird dem Baustein mitgeteilt, ob der externe oder der interne Oszillator verwendet wird. Da hier der interne Oszillator verwendet wird, liegt dieser Eingang (J12/13) auf Masse.

#### 7.4.1 Der Takt

Der Takt wird an einem synchronen Teiler durch drei geteilt und auf den Ausgang CLK (J12/8) gelegt. Diese Taktfrequenz von 9,54 MHz wird dem Prozessor zur Verfügung gestellt. Ein zweiter synchroner Teiler teilt die Taktfrequenz noch einmal durch zwei und legt diese auf den Ausgang PCLK (J12/2) (=Peripherial Clock). Die Taktfrequenz von 4,77 MHz wird einmal auf den NDR-Bus (ST2/30) gelegt und außerdem über zwei weitere 1:2 Teiler (J10) dem Timer zur Verfügung gestellt.

Die beiden Flip-Flops sind jeweils als 1:2 Teiler beschaltet; der Jumper JMP2 ist so eingestellt, daß der Taktausgang des zweiten Teilers (=1,19 MHz) auf die Takteingänge des Timers gelegt wird. Diesen Takt von 1,19 MHz benötigt der Timer zum Betreiben der Uhr.

## 7.4.2 Die Reset-Logik

Die RESET-Logik des Bausteines hat nur zwei Funktionen. Zum Einen hat der Eingang J12/11 einen Schmitt-Trigger Eingang, das heißt, daß an diesem Eingang ein analog ansteigendes Signal, wie es beim Einschalten oder beim Drücken der RESET-Taste S1 entsteht, an dem RC-Glied R1 und C2 anliegt. Zum Zweiten wird das RESET-Signal mit dem Takt (Prozessortakt) synchronisiert und invertiert, sodaß es am Ausgang J12/10 in der positiven Logik anliegt. Die Länge des RESET-Signales wird allerdings von dem schon erwähnten RC-Glied bestimmt. Die Zeit ist in etwa das Produkt aus R1 und C2 mal 0.8.

#### 7.4.3 Das READY-Signal

Die dritte Funktion dieses Bausteines ist die Synchronisation des READY-Signales. Die Logik bietet doch einige Möglichkeiten. Der Baustein stellt zwei READY-Eingänge zur Verfügung (J11/4 und J11/6), die über die beiden Eingänge -AEN (J11/3 und J11/7) freigegeben werden können. Die beiden Eingänge werden Oder-verknüpft, das heißt, wenn einer der Eingänge LOW ist (das bedeutet nicht "ready"), wird dieses Signal auf den Ausgang durchgeschaltet.

#### 7.4.4 Das WAIT-Signal

Nun sind aber auf diesem Baustein noch zwei nützliche Eigenschaften integriert: Zum Einen kann dieses READY-Signal über ein FLIP-FLOP mit dem Prozessortakt synchronisiert werden und auf den Ausgang J11/5 gelegt werden. Zum Zweiten kann aber dieses READY-Signal noch um einen Taktzyklus verzögert werden, es wird also ein WAIT-State eingefügt. Diese beiden Modi werden mit dem Eingang ASYNC (J11/15) gesteuert. In unserer Schaltung liegt ASYNC auf Masse, das heißt, daß ein WAIT-State eingefügt wird.

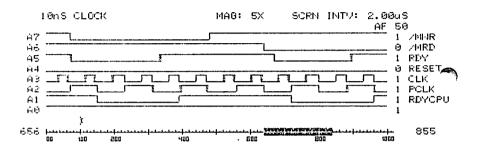

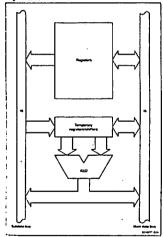

# Timing Diagramm CLK, PCLK, RESET, READY

#### 7.5 Der Bus-Controller

Der 8288, auf den weiter oben schon kurz eingegangen wurde, ist eigentlich nichts Anderes als ein Decoder mit einigen Besonderheiten. Der Decoderteil dieses Bausteines erzeugt aus den Statussignalen -SO, -S1 und -S2 (J1/26/27/28) die Steuersignale -MRD, -MWR, -IORD, -IOWR und -INTA nach obenstehender Wahrheitstabelle (Tabelle 1). Zusätzlich hat der Baustein noch die Eingänge CLK, -AEN, CEN und IOB. Mit Hilfe des CLK-Signals werden die oben erwähnten Steuersignale und die sonstigen Ausgänge synchronisiert.

Über den Eingang -AEN (Adress Enable) werden die Steuersignale MRD, MWR, usw. freigegeben oder gesperrt (hochohmig). Dies ist bei DMA-Zugriffen nötig. Der Eingang IOB dient dazu, den Baustein zwischen den beiden Bus-Modi (I/O-Bus Mode und System-Bus Mode) umzuschalten. In unserer Schaltung wurde dieser Eingang (J13/1) auf Masse gelegt, also auf System-Bus Mode. Der Eingang CEN (Command Enable) (J13/15) dient ebenfalls zur Freigabe der Steuersignale und der beiden Signale DEN und -PDEN. Dieser Eingang liegt hier auf HIGH, das heißt, die Signale sind freigegeben.

# 7.6 Der Daten- und Adressenmultiplex

Außer den Steuersignalen gibt es noch vier weitere Ausgänge, die zur Steuerung des Daten- und Adreßmultiplex der Prozessor-Signale AD0 bis AD7 dienen. Der Ausgang DEN (Data Enable J13/16) zeigt an, daß auf den Signalleitungen AD0 bis AD7 gültige Daten anliegen, wenn dieser Ausgang auf HIGH liegt. Der Ausgang DT/-R (Data Transmit/Receive) zeigt die Richtung des Datenflußes an. Ist dieses Signal LOW, werden Daten gelesen, ist das Signal HIGH, werden Daten geschrieben. Diese beiden Signale steuern den Datenbustreiber zum NDR-Bus (J14). Der Ausgang ALE (Adress Latch Enable) zeigt an, daß gültige Adressen auf den Adreßleitungen der CPU anliegen, auch daß auf den Signalleitungen AD0 bis AD7 im Moment Adressen anliegen. Dieses Signal wird dazu verwendet, die Adreßlatches mit den aktuellen Adressen zu laden (J15/11, J17/11 und J18/11). Der Ausgang MCE (Master Cascade Enable) oder -PDEN (Peripherial Data Enable) ist abhängig vom Eingang IOB. Da dieser Eingang auf LOW liegt, ist der Ausgang MCE aktiv. Dieser Ausgang dient zur Interruptabarbeitung, wird aber hier nicht benutzt.

# 7.7 Der Decodier-/Select-Logik

Der nächste Block, den wir näher durchleuchten wollen, ist die Dekodier- bzw. Selekt-Logik. Diese Logik ist in den beiden PALs J16 und J19 zusammengefaßt. Über J16 werden die I/O Bausteine dekodiert. Dazu werden an den Eingängen des Bausteines die Adressen A3 bis A9 (J16/1 bis J16/7) und die beiden Signale -IORD und -IOWR (J16/8 und J16/9) verwendet. Hier vielleicht noch kurz einige Erklärungen allgemein zum Thema I/O-Zugriff.

# 7.7.1 Die Select-Signale

Greift der Prozessor auf I/O zu, so aktiviert er die Adreßleitungen A0 bis A9 und das Signal -IORD oder -IOWR, je nachdem ob er einlesen oder ausgeben will. Auf den Adressen A0 bis A9 liegt die Adresse der I/O-Einheit, die sogenannte Portadresse. Die Dekodier-Logik hat nun die Aufgabe, aus dieser Portadresse und den Signalen -IORD und -IOWR ein Selekt-Signal für den I/O-Baustein zu erzeugen. An den Ausgängen dieser Logik liegen die Selekt-Signale für folgende Bausteine:

| -SNMI<br>-SPIO | (Select Non maskable Interrupt)<br>(Select Parallel Input Output) | J16/16<br>J16/15 |

|----------------|-------------------------------------------------------------------|------------------|

| -STIM<br>-SINT | (Select Timer) (Select Interrupt-Controller)                      | J16/14<br>J16/13 |

| -SELIO         | (Select Input Output)                                             | J16/12           |

#### 7.7.2 Die Portadressen

Bei der Selektierung der Standard I/O, wie z.B. Timer, Interruptcontroller und PIO, haben wir uns natürlich an die Standardadressen, die vom IBM-PC vorgegeben sind, gehalten. In der untenstehenden Tabelle sehen Sie die Portadressen der einzelnen Bausteine:

| Baustein             | Portadressen |

|----------------------|--------------|

| PIO                  | 60h7Fh       |

| Timer                | 40h5Fh       |

| Interrupt-Controller | 20h3Fh       |

| NMI                  | A0hBFh       |

| SELIO                | 00hFFh       |

Der Prozessor 8088 kann im Gegensatz zum Z80 nicht nur 256 I/O-Ports adressieren, sondern 1024. Deshalb werden hier auch die Adressen A8 und A9 zusätzlich verwendet. Außerdem tritt hier das Problem der Portdoppelbelegung auf, z. B. GDP64k und PIO. Diese Doppelbelegungen werden durch das sogenannte -SELIO-Signal verhindert. Wird auf die internen I/Os zugegriffen, muß auf die Adressen 00h bis FFh zugegriffen werden. Soll auf externe I/Os zugegriffen werden, müssen die Portadressen 100h bis 3FFh verwendet werden. Probleme treten dann auf, wenn später mit der Buskopplung PC-Baugruppen verwendet werden, die sich in der Portbelegung mit den NDR-Baugruppen überschneiden. Bei den Standardbaugruppen:

Hercules mit Bildschirm, Seriell-Adapter, OMTI Controller und Farbgraphikadapter

treten keine Probleme auf. Schwierigkeiten kann es lediglich mit der parallelen Druckerschnittstelle geben. Hier muß dann gewährleistet sein, daß keine GDP im System steckt, wenn eine Herculeskarte eingesetzt wird.

# 7.7.3 Die Decodierung der Speicherbereiche

Die Dekodierung der Speicherbereiche erfolgt durch den PAL J19. Dazu werden die Signale A14 bis A19, sowie die Steuersignale -MRD und -MWR benötigt. Analog zum I/O Zugriff wird beim Speicherzugriff vom Prozessor ebenfalls eine Adresse und eines der beiden Steuersignale angelegt. Die Select-Signale für die Speicher sind:

| -SELROM | (Select ROM)    | J19/13, |

|---------|-----------------|---------|

| -SELRAM | (Select RAM)    | J19/12, |

| -SELMEM | (Select Memory) | J19/14. |

Das Select Signal -SELROM selektiert das BIOS EPROM. Das -SELRAM Signal wählt den internen RAM (J31) aus. -SELMEM dient zur Auswahl des externen Speichers (nicht auf der CPU8088, z.B. ROA64, ROA256 oder RAM64/256).

# Adressen der verschiedenen Speicher

| Speicher | Adressen                                         |              | Speicherplatz |

|----------|--------------------------------------------------|--------------|---------------|

|          | F0000h FFFFFh<br>B0000h B3FFFh,<br>00000hB0000h, | BC000hBFFFFh | 64K<br>32K    |

|          | C0000h EFFFFh                                    |              | 950K          |

Außerdem übernimmt dieser Baustein noch die Invertierung der vom NDR-Bus kommenden Interruptsignale -INT, -NMI und Reserve (ST2/32/47/54).

# 7.8 Der Interrupt-Controller

Der Interrupt Controller 8259 besitzt 8 Interrupteingänge, auf denen die Interrupt-Anforderungen der einzelnen Blöcke (Tastatur, Paralleldrucker, zwei Asynchron-Adapter und der Zeitgeber) eintreffen.

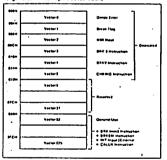

# 7.8.1 Der Ablauf eines Interrupts

Kurz noch einige Worte zum generellen Ablauf des Interrupt mit dem Controller 8259. Löst einer der 5 angeschlossenen Blöcke einen Interrupt aus, wird der INT-Ausgang des Controllers J8/17 aktiviert. Die CPU erkennt den Interrupt und quittiert diesen mit den Statussignalen -S0, -S1 und -S2 (siehe CPU8088). Der Bus Controller 8288 generiert aus dieser Statusmeldung das -INTA-Signal (Interrupt Acknowledge), das dem 8259 (J8/26) mitteilt, daß der Interupt erkannt wurde. Der 8259 erniedrigt das Priority Byte (Einfrieren des momentanen Status) und wartet, bis die CPU das zweite -INTA Signal generiert. Jetzt erkennt der 8259, daß die CPU bereit ist, den Interruptvektor entgegen zu nehmen. Der 8259 legt jetzt den Vektor auf den Datenbus und die CPU 8088 liest diesen ein und verzweigt in die entsprechende Interruptroutine.

# Belegung des Interruptcontrollers

| Eingang    | Priorität | Wer löst aus                |

|------------|-----------|-----------------------------|

| IRO (J8/1  | 8) 0      | Systemuhr                   |

| IR1 (J8/1  | 9) 1      | Tastatur (Zeichen steht an) |

| IR2 (J8/2  | 0) 2      | nicht belegt                |

| IR3 (J8/2  | 1) 3      | Asynchron Adapter 1         |

| IR4 (J8/2) | 2) 4      | Asynchron Adapter 2         |

| IR5 (J8/2: | 3) 5      | nicht belegt                |

| IR6 (J8/2  | 4) 6      | nicht belegt                |

| IR7 (J8/2  |           | Centronics Schnittstelle    |

Dabei ist 0 die höchste und 7 die niedrigste Priorität.

Treten nun aber zwei Interrupts gleichzeitig am 8259 auf, so muß der Controller erkennen, welchen er zuerst abarbeiten muß. Dazu kann dem 8259 eine Prioritätsliste übergeben werden, welcher Interrupt die höchste, die zweithöchste, usw. Priorität hat.

#### 7.8.2 Die Beschaltung

Auf die Beschaltung des 8259 soll noch kurz eingegangen werden. Die Eingänge IR0 bis IR7 sind die Interruptrequest-Eingänge von den Peripherieblöcken. Die Datenleitungen D0 bis D7, sowie die Signale -IORD, -IOWR und A0 sind Signale, mit deren Hilfe mit dem Bus kommuniziert werden kann. Mit -IORD und -IOWR wird festgelegt, ob in eines der 8259 Register geschrieben wird oder ob von ihnen gelesen wird. In welches Register geschrieben bzw. gelesen wird, hängt von A0 ab.

# Wahrheitstabelle Registerauswahl

| -IORD | -IOWR | AO | Register        |

|-------|-------|----|-----------------|

| o     | 1     | 0  | Statusregister  |

| 0     | 1     | 1  | Statusregister  |

| 1     | 0     | 0  | Commandregister |

| 1     | . 0   | 1  | Commandregister |

|       |       |    | •               |

Das Signal SP/-EN dient zur Steuerung des Datenbustreibers während des Anlegens des Interruptvektors. Hier wird dieses Signal dazu verwendet den Datenbustreiber (J14) zu sperren, um eine Datenkollision zu vermeiden. Die Eingänge CAS0 bis CAS2 dienen zum Kaskadieren von Interrupt Controllern. Insgesamt können bis zu 8 Bausteine angeschlossen werden. Diese drei Pins sind hier offen, da nur ein 8259 verwendet wird.

# 7.9 Der Timer

Der Timer 8253 beinhaltet drei Timer, die unabhängig voneinander gesteuert werden können. Der Ablauf der Timerfunktion hängt vom eingestellten Modus ab. Es gibt 6 verschiedene Modi, den Timerablauf festzulegen. Die einzelnen Modi sind im Datenblatt nachzulesen, ebenfalls die Programmierung des 8253.

Die Busschnittstelle beinhaltet die Datenleitungen D0 bis D7, die Signale -RD und -WR (J3/22/23) und die Adreßleitungen A0 und A1 (J3/19/20). Die 8 Register werden wie folgt adressiert:

| A0 | AI | -RD | -WR | Register              |

|----|----|-----|-----|-----------------------|

| 0  | 0  | 1   | 0   | Zähler 0 laden        |

| 1  | 0  | 1   | 0   | Zähler 1 laden        |

| 0  | 1  | 1   | 0   | Zähler 2 laden        |

| 1  | 1  | 1   | 0   | "Mode Wort" schreiben |

| 0  | 0  | 0   | 1   | Zähler 0 lesen        |

| 1  | 0  | 0   | 1   | Zähler 1 lesen        |

| 0  | 1  | 0   | 1   | Zähler 2 lesen        |

| 1  | 1  | 0   | 1   | nicht belegt          |

Die Eingänge GATE0, GATE1 und GATE2 sind Triggereingänge für die drei Timer. Die Eingänge CLK0, CLK1 und CLK2 sind die Takteingänge der 3 Zähler. Dieser Clock bestimmt die Grundzykluszeit der Zähler. Die Outputs OUT0, OUT1 und OUT2 sind die Ausgänge, die je nach eingestelltem Timermodus ein Strobe-Signal oder ein definiert langes Signal ausgeben.

In unserer Schaltung sind nur die beiden Timer 0 und 2 benutzt. Timer 0 dient dazu, die Softwareuhr des Rechners zu triggern. Dazu wird im Timer der Modus 2 verwendet. In diesem Modus wird der Timer mit einem bestimmten Wert (=65535) geladen und damit auch gestartet. Ist der Timer abgelaufen, wird ein Strobe-Signal ausgegeben, das auf den Interrupt-Controller (J8/18 Zeitgeber) gelegt wird. Mit der gewählten Taktfrequenz von 1,19 MHz erfolgen rund 18 Interruptanforderungen pro Sekunde (Die 'Triggerfrequenz' beträgt 18Hz). Die Interruptroutine macht dann nichts Anderes als nach jedem 18ten Aufruf den Uhrenstand um 1 Sekunde zu erhöhen.

Der zweite Timer dient zur Erzeugung der Lautsprecherfrequenz. Damit können durch Laden verschiedener Zählerwerte verschiedene Frequenzen ausgewählt werden und damit das ganze Tonspektrum abgedeckt werden.

Timer 1 ist unbelegt und kann nach Bedarf frei verwendet werden.

# Belegung des Timer 8253 (J3)

| Timer   | Belegung         |

|---------|------------------|

| Timer 0 | Systemuhr        |

| Timer 1 | nicht verwendet  |

| Timer 2 | Lautsprechertakt |

# 7.10 Die WAIT-Logik

Die WAIT-Logik des Rechners wurde beim Baustein 8284 schon kurz gestreift. Der zweite Teil dieser WAIT-Logik steckt in dem PAL J20. Die PAL-Logik ist so aufgebaut, daß bei I/O Zugriffen grundsätzlich zwei WAIT-Zyklen und bei externen Speicherzugriffen ein WAIT-Zyklus eingefügt wird. Zum Generieren der I/O-WAITs werden nur die Signale -IORD und -IOWR verwendet, zum Generieren des WAITs für externe Speicher werden die Signale -MRD, -MWR und -SELMEM verwendet. Außerdem wird natürlich ein WAIT, der vom NDR-Bus kommt, ebenfalls weitergeleitet. Das ebenfalls an den PAL gelegte -SELIO-Signal wird nicht verwendet. Der angelegte Takt (J20/1) steuert die internen Register des PALs, das heißt, die Periodendauer des Taktes entspricht einem WAIT-Zyklus.

# 7.11 Die Busanpassung

Ein weiterer Block ist die Busanpassung zum NDR-Computer (PAL 21). Die auf der Baugruppe erzeugten Steuersignale sind auf den Prozessor und auf den PC bezogen. Diese Steuersignale unterscheiden sich nur unwesentlich vom NDR-Bus, der auf den Z80-Prozessor zugeschnitten ist. Dies sind im wesentlichen die Signale:

Die vier Steuersignale -MRD, -MWR, -IORD, und -IOWR werden so verknüpft, daß die NDR-Signale -MREQ, -IORQ, -RD und -WR erzeugt werden. Außerdem werden diese Signale noch mit den Eingängen -SELIO und -SELMEM verknüpt, d.h. -RD und -WR sind nur aktiv, wenn -SELMEM oder -SELIO aktiv sind. -IORQ wird nur aktiv, wenn -SELIO aktiv ist. Das RESET Signal wird lediglich invertiert und auf den NDR Bus gelegt.

Außerdem erzeugt PAL J21 noch das Select-Signal für den Datenbustreiber J14. Der Datenbustreiber wird demnach nur aktiv, wenn das Signal DEN (Data Enable) aktiv ist und auf eine externe I/O oder einen externen Speicher zugreift und kein Interruptacknowledge-Zyklus abläuft. Außerdem wird noch das Banken-Signal über PAL J21 erzeugt. Das Banken-Signal wird bei jedem Speicherzugriff aktiviert.

# 7.12 Die Adreßpuffer

Der Vollständigkeit halber gehen wir hier noch kurz einmal auf die Adreßpuffer ein. Dies sind die drei Bausteine J15, J17 und J19. Sie haben im wesentlichen zwei Aufgaben. Zum Einen hat J15 die Aufgabe, die gemultiplexten Daten-Adreß-Leitungen AD0 bis AD7 so aufzusplitten, daß am Ausgang des Puffers nur die Adressen anliegen und zwischengespeichert werden, bis neue Adressen ausgegeben werden.

Die zweite Aufgabe dieser Puffer ist das "Treiben" (verstärken) der Adreßsignale. Gesteuert werden diese Adreß-Latches mit dem ALE-Signal (Adress Latch Enable). Der Eingang -OC (Output Control) gibt die Ausgänge der Latches frei. Hier liegt dieser Eingang auf Masse, d.h. die Treiber sind ständig frei.

# 7.13 Der Keyboard-Controller

Damit sind wir fast am Ende der eigentlichen CPU-Karte angelangt. Es fehlt nur noch der große Block des KEYBOARD-Controllers. Dieser Block umfaßt den parallelen I/O Baustein 8255 (J4), das Schieberegister 74LS322 (J5), das D-Flip-Flop 74LS74 (J9) und ein PAL (J11). Außerdem übernimmt der Keyboard Controller noch die Aufgabe, den Lautsprecher zu steuern. Ebenfalls in diesen Block integriert ist noch die NMI-Steuerung (Non Maskable Interrupt) für den 8087.

# 7.13.1 Die parallele Ein/Ausgabe

Der 8255 ist ein paralleler Schnittstellenbaustein mit drei 8 Bit breiten parallelen Schnittstellen. Diese drei Schnittstellen PA0 bis PA7, PB0 bis PB7 und PC0 bis PC7 sind sowohl als Eingänge als auch als Ausgänge definierbar. Diese Option kann im Steuerwortregister festgelegt werden.

Damit wären wir schon bei der Busschnittstelle und den Registern des 8255. Die Busschnittstelle ist bis auf das zusätzliche RESET-Signal exakt gleich wie die des Timers 8253. Die Register sind wie folgt zugänglich:

| -  |    |    |       |       |                    |

|----|----|----|-------|-------|--------------------|

|    | ۸0 | A1 | -IORD | -IOWR | Register           |

|    | 0  | 0  | 0     | 1     | Port A lesen       |

| 1  | 1  | 0  | 0     | 1     | Port B lesen       |

| 1  | 0  | 1  | 0     | 1     | Port C lesen       |

| ١  | 0  | 0  | 1     | 0     | Port A ausgeben    |

| ı  | 1  | 0  | 1     | 0     | Port B ausgeben    |

| ١  | 0  | 1  | 1     | 0     | Port C ausgeben    |

| ١  | 1  | 1  | 1     | 0     | Steuerwortregister |

| -1 |    |    |       |       | _                  |

Hier wird Port PA0 bis PA7 für die parallelen Tastaturdaten verwendet. Port PB wird für den Lautsprecher und für die Tastatur benötigt. Bit PB0 steuert den GATE Eingang des Timers (Timer 2, J3/16). Über PB1 ist es möglich, parallel zum Timer2 Lautsprecherdaten auszugeben. Auf PB6 wird der Keyboard-Clock ausgegeben, wenn der Rechner etwas an die Tastatur übermitteln will. Dieser Betrieb wird aber bei PCs nicht durchgeführt. Jedoch kann die PC-Tastatur über einen 20ms langen LOW-Impuls zurückgesetzt werden. Über PB7 wird das Schieberegister J5 gelöscht. Auf Port PC wird nur 1 Bit gelesen, dies ist der Lautsprechertakt auf PC5 (J4/12).

# Belegung der parallelen Ein/Ausgänge des 8255

| Ein/Ausgang | Belegung                                                                                                   |

|-------------|------------------------------------------------------------------------------------------------------------|

| PA0 bis PA7 | Tastaturdaten (System Scan Code), wenn PB7 = LOW oder DIL-Schalter, wenn PB7 = HIGH (hier nicht vorhanden) |

| PB0 (J4/18) | Lautsprecher Freigabe: LOW = gesperrt<br>HIGH = frei                                                       |

| PB1 (J4/19) | Timer 2: LOW = Takt aus,  HIGH = Takt ein  Takt (Frequenz) für Lautsprecher                                |

| PB2 bis PB5 | nicht verwendet                                                                                            |

| PB6 (J4/24) | Tastaturdatentakt bei Transfer Rechner> Tastatur<br>HIGH = Taktltg. hochohmig<br>LOW = Taktleitung LOW.    |

| PB7 (J4/25) | Auswahl Tastatur oder DIL-Schalter (siehe PA0 bis PA7)                                                     |

| PC0 bis PC4 | nicht verwendet                                                                                            |

| PC5 (J4/12) | Timer Kanal 2 (Einlesen des Lautsprechertaktes)                                                            |

| PC6 (J4/11) | GND*                                                                                                       |

| PC7 (J4/11) | GND*                                                                                                       |

<sup>\*:</sup> Die Eingänge PC6 und PC7 zeigen bei PCs im Normalfall einen I/O und Memory Parity Fehler an:

LOW = Kein Parity Fehler, HIGH = Parity Fehler. Da hier aber keine Paritätsprüfung gemacht wird, werden diese beiden Eingänge fest auf Masse gelegt.

Der in der Tabelle angesprochene DIL-Schalter ist bei PCs manchmal vorhanden und wird vom BIOS auch unterstützt. Physikalisch ist dieser aber auf unserer Baugruppe nicht vorhanden.

#### 7.13.2 Das Einlesen eines Zeichens