# GRAF computer GDP64HS

Die monochrome Standardgraphik- Karte für den

NDR- Computer und

mc- Computer

Ausgabe 3

Graf Elektronik Systeme GmbH 8960 Kempten - Tel.: 08 31 - 62 11

| Inhalt                                                           | Seite |

|------------------------------------------------------------------|-------|

| 1 Einführung                                                     | 3     |

| 1.1 Zum NDR-Computer                                             | 3     |

| 1.2 Wozu dient die Baugruppe                                     | 4     |

| 2. Technische Daten                                              | 5     |

| 3 Prinzipbeschreibung                                            | 6     |

| 3.1 Blockschaltbild                                              | 6     |

| 3.2 Datenübertragung zum Monitor                                 | 9     |

| 4 Aufbauanleitung                                                | 12    |

| 4.1 Stückliste des Komplettbausatzes                             | 13    |

| 4.2 Stückliste des Aufbausatzes                                  | 14    |

| 4.3 Aufbau Schritt für Schritt                                   | 15    |

| 5 Testanleitung                                                  | 18    |

| 5.1 Erste Prüfung ohne IC's                                      | 18    |

| 5.2 Test der GDP 64k im System<br>5.3 Test und Beispielprogramme | 22    |

| Beschreibung zu den Testprogrammen                               | 22    |

| Alphazeichen                                                     | 23    |

| Graphik                                                          | 24    |

| Vektoren zeichnen                                                | 25    |

| Demo für 680xx                                                   | 26    |

| 5.4 Jumperstellungen                                             | 27    |

| 6 Fehlersuchanleitung                                            | 28    |

| 7 Schaltungsbeschreibung                                         | 30    |

| 7.1 Wie funktioniert die Baugruppe ?                             | 30    |

| 7.2 Hinweise zum Monitoranschluß                                 | 40    |

| 8 Anwendungsbeispiel                                             | 41    |

| 8.1 Direkte Eingabe von Grafikzeichen                            | 41    |

| 8.2 Beispiel als Basic - Programm                                | 42    |

| 8.3 Beispiel in Turbo - Pascal                                   | 42    |

| 8.4 Hardcopyprogramm unter CP/M 2.2                              | 43    |

| 8.5 Hardcopyprogramm für 680xx<br>8.6 Hardscroll- Demo für 680xx | 56    |

| 0.0 Haldscioli- bene lai oooka                                   | -     |

| 9 Diverses                                                       | 64    |

| 9.1 Ausblick                                                     | 64    |

| 9.2 Kritik<br>10 Unterlagen zu den verwendeten IC's              | 64    |

| 10 Unterlagen zu den verwendeten IC's                            | 65    |

| 10.1 TTL-IC'S                                                    | 65    |

| 10.2 Der Grafik Prozessor EF 9366                                | 83    |

| 11 Literatur                                                     | 90    |

| Anhang A: Schaltplan                                             | 91    |

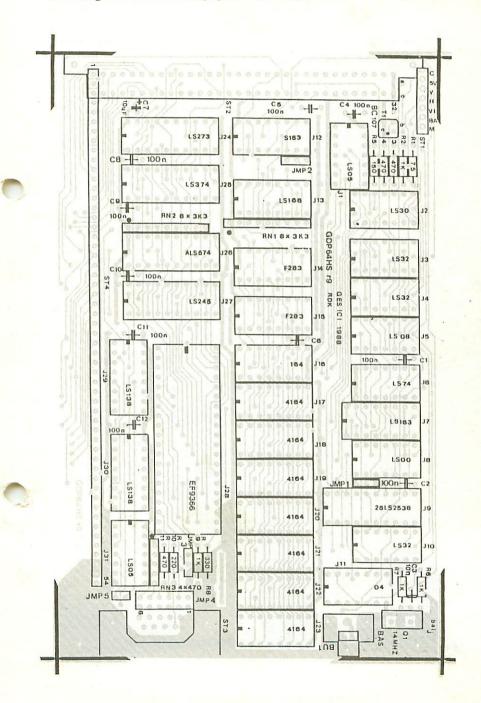

| Anhang B: Bestückungsplan                                        | 94    |

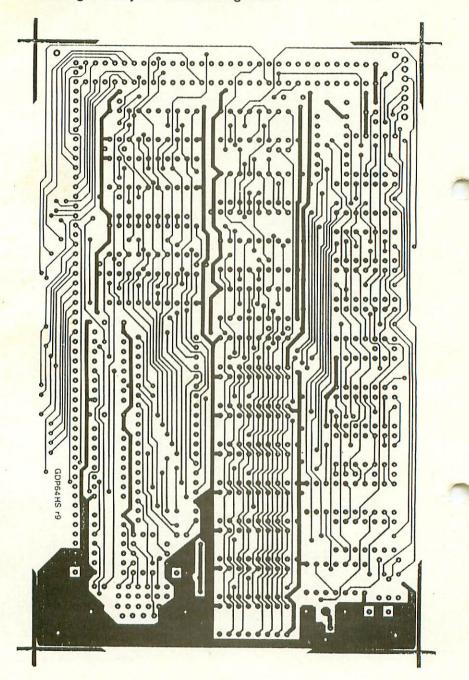

| Anhang C: Best Plan mit Layout, B- Seite                         | 95    |

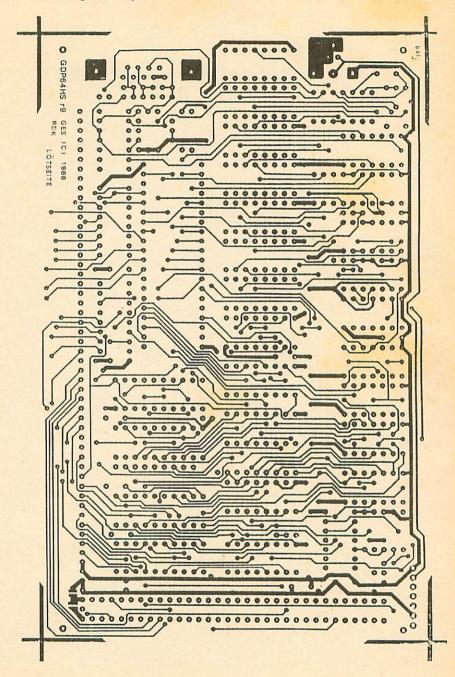

| Anhang D: Layout Bestückungsseite                                | 96    |

#### 1. Einführung

#### 1.1 Zum NDR-Computer

Der NDR-Computer wird in der Fernsehserie "Mikroelektronik - Mikrocomputer selbstgebaut und programmiert " aufgebaut, erklärt und in Betrieb genommen. Diese Serie wird vom Norddeutschen Rundfunk und vom Bayerischen Fernsehen ausgestrahlt. Es werden bald auch die Regionalsender anderer Bundesländer die Sendung in ihr Programm aufnehmen.

Zur Serie gibt es einige Begleitmaterialien, es ist daher nicht unbedingt notwendig, die Fernsehserie gesehen zu haben, um den NDR-Computer zu bauen und zu begreifen:

- Bücher:

Rolf-Dieter Klein,

"Rechner modular"

ISBN 3-7723-8721-7, DM 68,erschienen im Franzis-Verlag, München

Bestellnummer: 10991

Rolf-Dieter Klein,

"Die Prozessoren 68000 und 68008"

Rechnerarchitektur und Sprache im NDR-KLEINComputer

ISBN 3-7723-7651-7, DM 78.erschienen im Franzis-Verlag, München

- Zeitschriften "mc" und "ELO" des Franzis-Verlages

- Zeitschrift "LOOP" der Firma Graf Elektronik Systeme

- Videocassetten:

lizensierte Originalcassetten für den privaten Gebrauch. Auf diesen zwei Cassetten sind die 26 Folgen der Fernsehserie enthalten.

Systeme: VHS, Beta, Video 2000 Preise: siehe gültige Preisliste

#### 1.2 Wozu dient die Baugruppe

Die Baugruppe GDP64HS ist das Bindeglied zwischen dem Mikrocomputer (SBC 2, SBC 3, CPU 680xx oder CPU Z80) und einem Monitor. Sie ermöglicht es einen Monitor mit BAS - Anschluß oder einen TTL- Monitor anzuschliessen. Nun ist es möglich Arbeitsschritte, die der Computer durchführt, auf dem Monitor anzuzeigen, Graphiken darzustellen oder Einblick in das Innenleben des Computers zu bekommen (Speicherbelegung, Kontrolle der Eingaben). Die GDP64HS kann zudem noch sogenannte Hardcopys erstellen, d.h. der Bildschirm wird mit Hilfe eines Druckers auf ein Blatt Papier kopiert.

Da jeder Bildpunkt auf dem Monitor ansprechbar sein muß, wird bei einer Bildebene von 256 x 512 Bildpunkten ein eigener Speicher von 16 KByte benötigt, wenn jeder Bildpunkt ein Bit beansprucht. Da aber vier unabhängige Bildebenen aufgebaut werden können, braucht man demnach einen Speicherplatz von 64 KByte. Dieser ist in 8 x 64 KBit Speichern organisiert.

In diesem Speicher wird jeweils das gesamte Bild abgespeiseriell alle 20 ms abgerufen (50 mal in der chert und dadurch entsteht ein stehendes Bild. Die Verwal-Sekunde); tung des Speicherbereiches (Abruf des Bildes , Refresh...) übernimmmt der auf der GDP64HS befindliche Graphik-Prozessor Mit dem Mikrocomputer können per Datenbus Befehle 9366. z.B. Schreiben eines Zeichens, Größe übermittelt werden, des gewünschten Zeichens, Form des Zeichens, Lage und Position des Zeichens auf der Bildebene, Auswahl einer der vier Bildebenen . Dieser Prozessor ermöglicht es auch schnelle Graphik darzustellen (Blockgraphik und Vektoren). Durch Definition von verschiedenen Vektoren ist es möglich, Linien (Vektoren) in jede Richtung und in jeder Größe zu zeichnen .

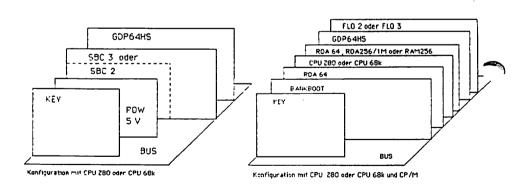

Verschiedene Konfigurationen mit der GDP64HS (Bild 1):

#### 2. Technische Daten

Spannungsversorgung: +5V

Stromaufnahme: 500 mA

Busformat: NDR - Bus 54-poliq

ECB - Bus 64-poliq

Leiterplattenformat: 160mm x 100mm (Europakarte)

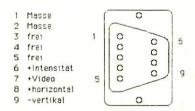

1.BAS (beinhaltet HS, VS und VIDEO - Signal) Ausgang:

2.TTL - Ausgang: HS, VS, VIDEO (invertierbar) z.B. IBM Monitor

EF 9366 (Thomson-CSF) Graphik - Controller:

-kann 4 Seiten bedienen, wobei in eine qeschrieben und zugleich eine weitere

gelesen werden kann.

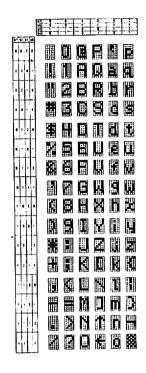

-integrierter ASCII- Zeichensatz

-Graphikbefehle \* Kurzvektoren

\* Vektoren

\* Blockgraphik 5x8 und 4x4

8 x 64k RAM (dynamisch) Speicher:

Modify (zerstörungsfreies sonstige Funktionen: Read Write Zeichnen auf dem Bildschirm)

- Hardcopy (Rücklesen des Bildschirminhaltes und Ausgabe auf einen Drucker)

- Hardscroll (Scrollen des Bildschirms mit Hilfe der Hardware, d.h. die Adressen des Bildschirmspeichers werden hardwaremäßig aufaddiert.

#### 3. Prinzipbeschreibung

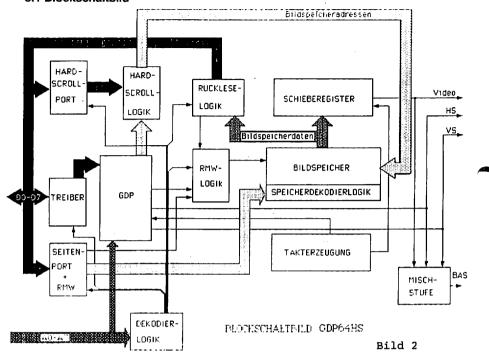

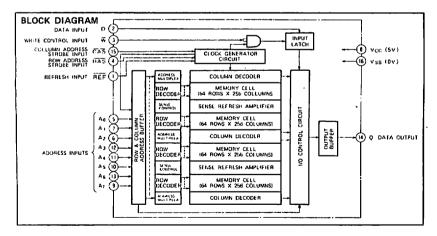

#### 3.1 Blockschaltbild

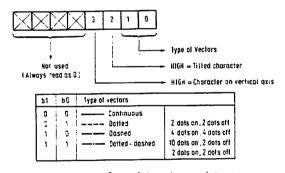

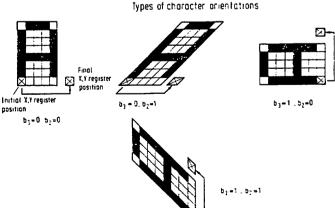

Von der Haupt- CPU (z.B. von der CPU68008) wird über die Adressleitungen AO...A3 eines der 16 Register der Neben- CPU (hier EF 9366) angewählt. Soll z.B. ein Vektor gezeichnet werden, so teilt man dem Graphik-Prozessor lediglich den Anfangs- und Endpunkt mit. Die Zwischenwerte werden von ihm selbst berechnet und dann in den Speicher abgelegt.

Der interne Aufbau des Speichers wird durch den Grafikprozessor und sekundär durch die Speicherdekodierlogik organisiert. Im Speicher steht dann die Information, die später auf dem Bildschirm erscheint.

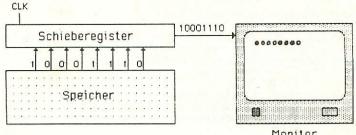

Beispiel: Wir verfolgen das Auslesen eines Bytes vom Speicher zum Monitor (z.B. 10001110)

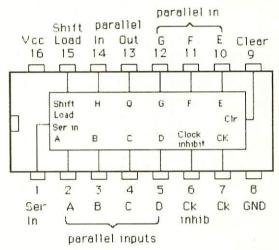

Das Byte steht am Ausgang des Speichers und wird bei aktivieren des Signals SH/L (Shift Load, am Schieberegister) parallel in das Schieberegister eingelesen. Hier wird das Signal mit dem Punktetakt (14 MHz, CLK) verknüpft und seriell (in der Punktfolge 10001110) an den Monitor hinausgeschoben. Da jedes Bit einen Bildpunkt darstellt, werden jetzt 8 Punkte auf dem Bildschirm angezeigt. Ein dunkler Punkt entspricht einer 1 und ein heller einer 0. (ebenfalls in der Reihenfolge 10001110). Siehe Bild 3 auf der nächsten Seite.

Monitor Bild 3

Der Speicher ist für 4 Seiten aufgebaut, die durch die Seitenumschaltung ausgewählt werden können. Es kann in eine Seite geschrieben und zugleich eine weitere gelesen werden. Das aus dem Schieberegister kommende Videosignal geht entweder direkt zum Monitor (TTL) oder zum Videomischer. In dieser Mischstufe wird das Video-Signal mit horizontalen und vertikalen Synchronisationssignalen (HS und VS) so aufbereitet, daß es danach als BAS-Signal (siehe 3.2.2) zur Verfügung steht.

Will man eine Hardcopy erstellen, muß man ähnlich der Datenübertragung zum Monitor den Bildspeicher auslesen. Das Auslesen des Bildschirmspeichers läuft parallel zum Display (Ausgeben der Bildschirminformation). Durch einen Befehl an den Graphikprozessor kann jeweils ein Byte des Bildschirmspeichers gelesen werden und im Arbeitsspeicher abgelegt werden. Durch eine Druckerroutine kann nun das Bild auf einen Drucker ausgegeben werden. Das Auslesen des Bildschirmspeichers ist auch für andere Aufgaben sehr nützlich (z.B. Vergleich von Bildschirmseiten, Abfrage des Maus-Zeigers für Graphikprogramme, Windowtechnik, usw.)

Hardware-Scroll-Logik dient zum Rollen (Scroll) Bildschirms. Bei der bisherigen GDP64k wurde der Scroll softwaremäßig erzeugt. Sollte der Bildschirm Textdarstellung um eine Textzeile nach oben gescrollt werden, so mußte das gesammte Bild noch einmal aufgebaut (um eine Zeile versetzt). Dadurch war der Scroll natürlich sehr langsam und nur zeilenweise (Textzeile = 8 Bildschirmzeilen) möglich. Der Hardware Scroll behebt diese beiden Mängel. Dabei wird der Bildschirmspeicher beim Scrollen nicht mehr verändert, sondern nur die Adressierung Bildschirmspeichers. Dies wird durch zwei Addierer erledigt, die lediglich die Bildspeicheradressen, die vom Graphikprozessor kommen mit einer Scrolladresse, die über 61 ausgegeben werden kann, aufaddiert und damit die Bildspeicheradresse erzeugt. Dadurch kann der hirm zyklisch gescrollt werden, natürlich mit einer Bildschirm zyklisch gescrollt werden, größeren Geschwindigkeit und zeilenweise (fließender Übergang).

Mit Hilfe des RMW-Modus kann man einfach bewegte Bilder erzeugen, da bei Schreibvorgängen in den Bildspeicher (=Monitor) alle Punkte komplementiert werden. Wenn z.B. ein Punkt gesetzt war, so wird er gelöscht, wenn er nicht gesetzt war, so wird er eingeschrieben. Der größte Vorteil des RMW-Modus ist, daß zerstörungsfrei gezeichnet werden kann. Dies ist z.B. nötig, um einen Maus-Zeiger oder ein Fadenkreuz auf einer Graphik oder einem Bild darzustellen,

ohne das Hintergrundbild zu zerstören.

Die Dekodierlogik mit den Adressen A4...A7, den Signalen IORQ und M1 wird benötigt, um die GDP64HS bei I/O- Zugriff von 70...7F (Graphikprozessor) und 60...6F (Seitenport, RMW=Mode, Hardcopy und Hardscroll) anzusprechen.

Die Takterzeugung stellt alle benötigten Frequenzen (Pixelclock, Clock für Schieberegister, Takte für die Adressierung der Speicher ) aus dem Grundtakt von 14 MHz her.

#### 3.2 Datenübertragung zum Monitor:

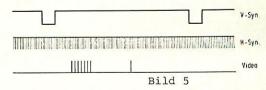

#### 3.2.1 Prinzip der Signale HS, VS und VIDEO.

HS- Signal: (Horizontal- Synchronisation) Dieses Signal ist für die Zeilensynchronisation zuständig. Der Bildschirm wird veranlaßt, mit dem Schreiben einer Zeile so lange zu warten, bis die zu Übertragende Information am VIDEO- Ausgang bereitgestellt ist. Wie der Name des Signales schon andeutet, wird das Übertragen der Daten und das Schreiben der Daten auf den Bildschirm synchronisiert.

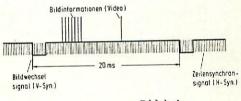

VS- Signal: (Vertikal- Synchronisation) Dieses Synchronisationssignal veranlaßt einen neuen Bildschirmaufbau, der alle 20 ms stattfindet. Der Schreibstrahl des Bildschirms fährt also von der rechten unteren Ecke in die linke Obere und wird in dieser Zeit ausgeblendet. Während dieses Vorganges kann keine Information geschrieben (also nichts auf dem Bildschirm dargestellt ) werden.

VIDEO- Signal: Es besteht aus High- und Low- Signalen die Bildinformation wiederspiegeln. Will man dieses Signal ansehen, verwendet man am besten ein Oszilloskop.

#### 3.2.2 Monitor mit BAS - Signal:

Das BAS - Signal wird bei normalen Monitoren über eine einzige Leitung übertragen und setzt sich aus den Einzelsignalen HS + VS + Video zusammen. Die Signale HS(bzw VS) und das Videosignal stehen im Verhältnis 1 zu 2.

Bild 4

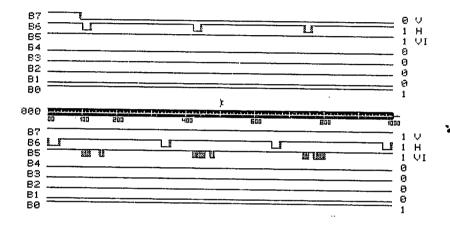

#### 3.2.3 Monitor mit TTL-Signal z.B. IBM - Monitor:

Hier werden die Signale HS, VS und Video über verschiedene Leitungen zum Monitor übertragen. (siehe rechts, prinzipieller Verlauf der Signale ohne Angabe der Zeiten).

Beispiel: Eine Originalaufnahme der drei Signale HS, VS und Video mit den Logik-Analyser erstellt:

Im ersten Diagramm erkennt man das VS- Signal, darunter das Signal HS und das VIDEO-Signal(VI). Wie daraus zu ersehen ist, wird während des HS-Signales keine Bildinformation geschrieben. Wird der HS- Impuls aktiv, wird in der nächsten Zeile weitergeschrieben. Das VS-Signal leitet den Aufbau eines neuen Bildes ein.

Bild 6

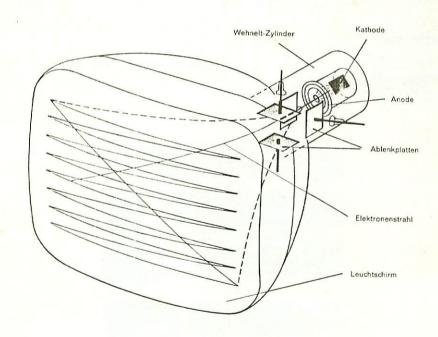

#### 3.2.4 Wie funktioniert ein Monitor ?

Der Monitor (Brownsche Röhre) besteht aus einer Kathode einer Fokussiereinrichtung (Wehnelt- Zylinder und Anode), Ablenkplatten für horizontale und vertikale Ablenkung und einer auf der Röhreninnenseite aufgetragenen Leuchtschicht.

Von der Kathode werden Elektronen ausgesendet, die von der Fokussiereinrichtung gebündelt werden. Die Ablenkplatten sorgen in horizontaler sowie in vertikaler Richtung für die nötige Ablenkung des Elektronenstrahles, damit jeder Punkt des Bildschirms erreicht wird.

Trifft der Elektronenstrahl an der Frontseite des Bildschirms auf (auf die Leuchtschicht ) so beginnt der angestrahlte Punkt zu Leuchten. Der ausgesandte Elektronenstrahl muß sehr scharf gebündelt sein, um eine hohe Auflösung zu erreichen.

Bild 7

#### 4. Aufbauanleitung

#### CMOS-Warnung:

CMOS-Bausteine sind hochempfindlich gegen elektrostatische Aufladung! Bewahren oder transportieren Sie CMOS-Bausteine nur auf dem leitenden Schaumstoff! Alle Pins müssen kurzgeschlossen sein.

Tip: Fassen Sie an ein geerdetes Teil (z.B. Heizung, Wasserleitung) bevor Sie einen Baustein berühren.

Bitte beachten Sie hierzu auch den Artikel "Schutzmaßnahmen für MOS-Schaltungen" in unserer Zeitschrift LOOP3.

### 4.1 Stückliste des Komplettbausatzes GDP64HS

| zahl                                                     | Nr.                                                                                                                                                                              | Position<br>im Plan                                                                              | Bezeichnung                                                                                                                                                                  | Bemerkungen                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1                                                        | 11229<br>11232                                                                                                                                                                   |                                                                                                  |                                                                                                                                                                              | Leiterplatte GDP64HS<br>Handbuch                                                                                                                                                                                                                                                                                             |  |  |  |  |

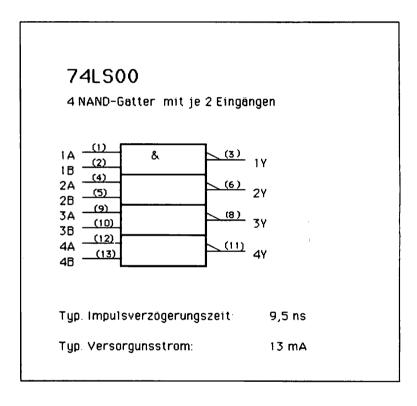

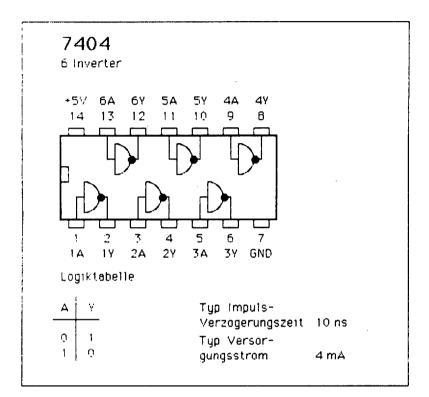

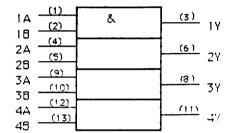

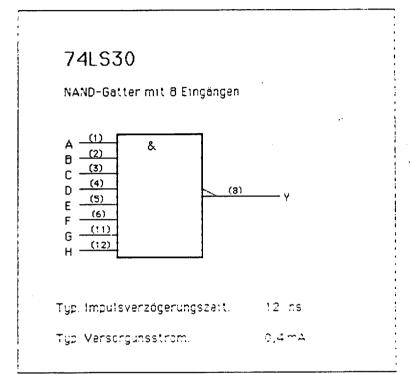

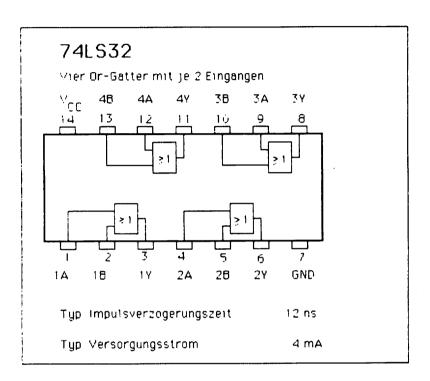

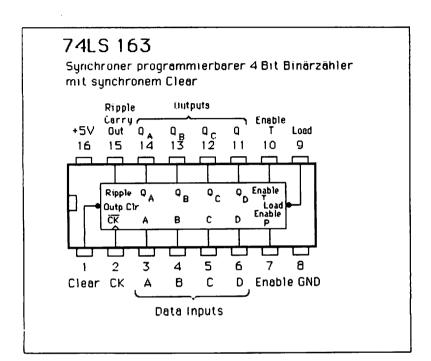

| 2<br>1<br>1<br>1<br>1<br>1<br>3<br>1<br>1<br>2<br>1<br>1 | 60082<br>60080<br>60104<br>60101<br>60075<br>60033<br>60014<br>60137<br>60121<br>10806<br>60098<br>60094<br>60115<br>10806<br>60118<br>60120<br>60120<br>60120<br>60126<br>61126 | J13<br>J7<br>J8<br>J11<br>J16J23<br>J6<br>J3,J4,J10<br>J9<br>J12<br>J29,J30<br>J27<br>J28<br>J24 | 74 LS 08 74 LS 05 74 LS 166 74 LS 163 74 LS 00 7404 4164, 200ns 74 LS 32 25 LS 2538 74 LS 153 74 LS 138 74 LS 245 EF 9366 74 LS 273 74 LS 283 74 LS 383 74 LS 374 74 ALS 574 | Sechs Inverter 8-Bit Schieberegister synch. 4-Bit Zähler 4 NAND Gatter 6 Inverter Dynam. RAM 64 kBit D-Flip Flop mit Preset Vier OR-Gatter 3 zu 8 Decoder 4 zu 1 Multiplexer 3 Bit Binärdekoder 8 fach Bus Transreceiver Graphik-Processor 8 Bit D-Register 8-fach NAND 4 Bit Volladdierer 8 Bit Datenlatch 8 Bit Datenlatch |  |  |  |  |

| 10<br>15<br>5                                            | 60183<br>60185<br>60187<br>60193                                                                                                                                                 | SO 14<br>SO 16<br>SO 20<br>SO 40                                                                 | 14-polige IC-Fassu<br>16-polige IC-Fassu<br>20-polige IC-Fassu<br>40-polige IC-Fassu                                                                                         | ang<br>ang                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 1<br>1<br>1<br>1<br>3<br>4                               | 60665<br>60621<br>60631<br>60643<br>60651<br>60626                                                                                                                               | R1<br>R5<br>R10<br>R8<br>R3,R4R11<br>R2,R6,R7,R9                                                 |                                                                                                                                                                              | Widerstand 75 Ohm Widerstand 150 Ohm Widerstand 220 Ohm Widerstand 330 Ohm Widerstand 470 Ohm Widerstand 1000 Ohm                                                                                                                                                                                                            |  |  |  |  |

| 2                                                        | 60518<br>60958                                                                                                                                                                   | RN1,RN2<br>RN3                                                                                   | 8X3,3,K<br>4x470 Ohm                                                                                                                                                         | Netzwerkwiderstand<br>Netzwerkwiderstand                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 1<br>11                                                  | 60248<br>60239                                                                                                                                                                   | C7<br>C1C6,<br>C8C12                                                                             | 10 uF,Tantal ELKC                                                                                                                                                            | auf Polung achten!<br>Keramikkondensator                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 1                                                        | 60590                                                                                                                                                                            | T1                                                                                               | BC 107                                                                                                                                                                       | Transistor                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 1                                                        | 60166                                                                                                                                                                            | Q1                                                                                               | Quarz 14.00 MHz                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 1<br>1<br>1<br>1<br>1                                    | 60499<br>60725<br>10787<br>10405<br>10406<br>10097                                                                                                                               | ST1<br>ST3<br>ST2<br>ST4<br>ST4<br>BU1                                                           | 7-polige Stiftleis<br>9-polige D-Sub-Buc<br>ECB-Bus 64-polig<br>NDR - Bus 18-polig<br>NDR - Bus 36-polig<br>Monitor Buchse Cin                                               | chse<br>oder<br>g, gewinkelt und<br>g, gewinkelt                                                                                                                                                                                                                                                                             |  |  |  |  |

#### 4.2 Stückliste des Aufbausatzes GDP64k-GDP64HS

| An-<br>zahl           | Art<br>Nr.                       |                                                           | Bezeichnung                                                                                                                    | Bemerkungen                                                                                                                                   |

|-----------------------|----------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>1<br>2           |                                  | J5<br>J3,J4,J10<br>J29,J30<br>J2<br>J14,J15<br>J25<br>J26 | 74 LS 138<br>74 LS 30<br>74 LS 283                                                                                             | Leiterplatte GDP64HS Handbuch 4 AND-Gatter Vier OR-Gatter 3 Bit Binärdekoder 8-fach NAND 4 Bit Volladdierer 8 Bit Datenlatch 8 Bit Datenlatch |

| 10<br>15<br>5<br>1    | 60183<br>60185<br>60187<br>60193 | SO 16                                                     | 14-polige IC-Fassu<br>16-polige IC-Fassu<br>20-polige IC-Fassu<br>40-polige IC-Fassu                                           | ng<br>ng                                                                                                                                      |

| 1<br>1<br>1<br>3<br>4 | 60643                            | R1<br>R5<br>R10<br>R8<br>R3,R4R11<br>R2,R6,R7,R9          |                                                                                                                                | Widerstand 75 Ohm<br>Widerstand 150 Ohm<br>Widerstand 220 Ohm<br>Widerstand 330 Ohm<br>Widerstand 470 Ohm<br>Widerstand 1000 Ohm              |

| 2<br>1                | 60518<br>60958                   | RN1,RN2<br>RN3                                            | 8X3,3,K<br>4x470 Ohm                                                                                                           | Netzwerkwiderstand<br>Netzwerkwiderstand                                                                                                      |

| 1<br>11               | 60248<br>60239                   | C7<br>C1C6,<br>C8C12                                      | 10 uF,Tantal ELKO<br>100 nF                                                                                                    | auf Polung achten !<br>Keramikkondensator                                                                                                     |

| 1                     | 60590                            | T1                                                        | BC 107                                                                                                                         | Transistor                                                                                                                                    |

| 1                     | 60166                            | Q1                                                        | Quarz 14.00 MHz                                                                                                                |                                                                                                                                               |

| 1<br>1<br>1<br>1<br>1 | 10405                            | ST1<br>ST3<br>ST2<br>ST4<br>ST4<br>BU1                    | 7-polige Stiftleis<br>9-polige D-Sub-Buc<br>ECB-Bus 64-polig<br>NDR - Bus 18-polig<br>NDR - Bus 36-polig<br>Monitor Buchse Cin | hse<br>oder<br>, gewinkelt und<br>, gewinkelt                                                                                                 |

## 4.3 Aufbau Schritt für Schritt des GDP64HS Komplettbausatzes bzw. des Aufbausatzes

Auf einer Seite der Leiterplatte steht der Hinweis "Lötseite"; auf dieser Seite wird ausschließlich gelötet. Die Bauteile sind nur auf der anderen Seite (der Bestückungsseite) aufzustecken.

Beim Einlöten der Bauelemente beginnt man am besten mit den ganz flachen Bauelementen. Bevor Sie jedoch beginnen sollten Sie sich Ihren Bestückungsdruck genau ansehen und die Bauelemente mit der Stückliste vergleichen. Eventuell fehlende Bauteile sollten Sie sofort reklamieren.

Demnach sollten Sie alle liegenden Widerstände zuerst bestücken. Dies sind die Widerstände R1 bis R11. Diese Widerstände sind durch Farbcodes zu indentifizieren:

| Widerstand     | Widerstandswert | Farbcode             |  |  |  |

|----------------|-----------------|----------------------|--|--|--|

| R1             | 75 Ohm          | violett-grün-schwarz |  |  |  |

| R2, R6, R7, R9 | 1 kOhm          | braun-schwarz-rot    |  |  |  |

| R3, R4, R11    | 470 Ohm         | gelb-violett-braun   |  |  |  |

| R5             | 150 Ohm         | braun-grün-braun     |  |  |  |

| R8             | 330 Ohm         | orange-orange-braun  |  |  |  |

| R10            | 220 Ohm         | rot-rot-braun        |  |  |  |

Der vierte Strich kennzeichnet die Toleranz und bei diesen Widerständen immer "gold".

Gehen Sie beim Einlöten der Widerstände folgendermaßen vor: Anschlußdrähte der Widerstände rechtwinkelig nach unten biegen und in den entsprechenden Platz auf der Leiterplatte stecken. Achten Sie bitte darauf daß die Widerstände auf der Leiterplatte aufliegen. Auf der Lötseite sollten Sie die überstehenden Enden leicht abbiegen und dann mit einem Seitenschneider abschneiden und verlöten.

Wenn Sie die Baugruppe für den NDR-Computer aufbauen, sollten Sie jetzt die 54-polige abgewinkelte Stiftleiste bestücken. Die Stiftleiste wird als 18-polige und als 36polige Stiftreihe geliefert. Beim Bestücken sollten Sie folgendermaßen vorgehen: Beide Stiftleisten mit abgewinkelten Ende in die vorgesehenen Bohrungen (ST4) stecken; dann die Leiterplatte umdrehen und 4 bis 5 Punkte (an den Enden und in der Mitte einige) verlöten. Jetzt sollten Sie erst auf der Bestückungsseite kontrollieren, ob Steckerleiste parallel geraden Stifte der Leiterplatte liegen und ob sich zwischen den Lötpunkten "Bäuche" gebildet haben. Sollte einer dieser beiden Defekte vorliegen können Sie dies jetzt noch problemlos beheben und dann die restlichen Pins verlöten.

Ist die Steckerleiste bestückt, kommt die arbeitsintensivste Bestückung: Die IC-Sockel. Bei den IC-Sockel gibt es eigentlich nur eines zu berücksichtigen und das ist die richtige Polarisation der Sockel. Jeder Sockel ist mit einer Kerbe versehen, die Pin 1 markiert. Auf dem Bestückungsdruck ist ebenfalls eine Kerbe bei jedem IC-Sockel aufgedruckt. Diese beiden Kerben müssen übereinstimmen (siehe Abb.).

Stecken Sie nun alle IC-Sockel auf. Achten Sie darauf, daß Sie nicht einen 14-poligen in den Platz eines 16-poligen stecken usw. Sind alle Sockel aufgesteckt, ist es hilfreich wenn Sie nach folgender Beschreibung vorgehen:

Legen Sie nun eine feste Pappe, ein Stück Holz oder etwas ähnliches auf alle Bauelemente und drehen dies unter festem andrücken der Pappe mit der Leiterplatte herum und löten von jedem IC-Sockel zwei diagonal gegenüberliegende Pins an. Bevor Sie die restlichen Pins verlöten, sollten Sie auf der Bestückungsseite noch einmal kontrollieren, ob alle Sockel richtia gesteckt worden sind und ob alle auf Leiterplatte aufliegen.

späteres Ändern macht meistens vielmehr Mühe und führt ungeübten Aufbauern oftmals zur Zerstörung Leiterplatte (Leiterbahnen werden abgerissen oder Durchkontaktierungen zerstört usw.).

Die Keramikkondensatoren C1 bis C6 und C8 bis C12 sind ungepolt; sie brauchen hier also nicht auf die Polung zu achten.

Beim Einlöten des Tantalkondensators C7 achten Sie bitte auf richtige Polung. Das "+" auf dem Kondensator muß mit dem "+" auf dem Bestückungsdruck übereinstimmen.

Beim Transistor muß auf die Anschlüsse E,B,C geachtet werden. Der Transistor hat an seinem Umfang eine "Nase". Der PIN, der dieser Nase am nächsten kommt, ist der Emitter (siehe Abb.)

Transistor von unten gesehen Bestückungsdruck

Der Transistor sollte nicht sehr tief hineingesteckt werden, da sonst die Hitze des Lötkolbens ihn zerstören könnte.

Zum Schluß werden die Buchsen und der Quarz bestückt. Beim Einlöten der BAS-Buchse BU1 ist darauf zu achten, daß diese ganz auf der Leiterplatte aufliegt. Die Buchse sollte fest aufliegen, dann erst kann sie eingelötet werden.

Der Schwingquarz ist nicht gepolt und kann somit nicht falsch herum eingelötet werden. Der Quarz kann, wenn er stehend stört auch nach folgender Abb. gelegt werden. Allerdings müssen Sie dann beim Bestücken des Haltewinkels den Quarz so legen, daß die Schraube für diesen noch Platz findet. Das Gehäuse des Quarzes darf Kontakt mit der Schraube bzw. mit Masse haben.

Abb. Einlöten des Quarzes Die Stecker ST1 und ST3, sowie die Jumper JMP1 bis JMP5 werden nicht bestückt. Die Jumper sind auf der Lötseite der Leiterplatte voreingestellt.

Sollten Sie die GDP64HS für den ECB-Bus aufgebaut haben, müssen Sie jetzt noch die 64-polige Messerleiste (ST1) bestücken, und die in folgender Abbildung durch Pfeil gekennzeichnete Brücken auf der Lötseite schließen.

#### Rückwandblech:

Wollen Sie diese Baugruppe in das Gehäuse GEH3 einbauen, so wird ein passendes Rückwandblech benötigt. (Bitte gesondert bestellen) #11211

#### 5. Testanleitung

#### 5.1 Erste Prüfung ohne IC's Komplettbausatz bzw. Aufbausatz

Die Leiterplatte ist bis jetzt erst mit den Sockeln und mit den passiven Bauelementen bestückt. Mit diesem Aufbau wird der erste Test durchgeführt.

Zu diesem Test muß die Baugruppe in den Bus gesteckt werden. Achten Sie beim Einstecken in den Bus, daß Sie die Baugruppe richtig herum einsetzen. Ein falsches Einstecken, z.B. um ein Pin zu weit rechts kann zu Kurzschlüssen führen und kann Bauelemente zerstören.

Nach dem Einstecken der Leiterplatte muß der Rechner weiter problemlos funktionieren. Falls nein - weiter im Kapitel 6.

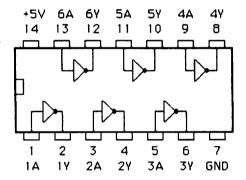

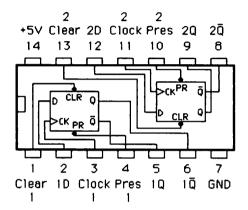

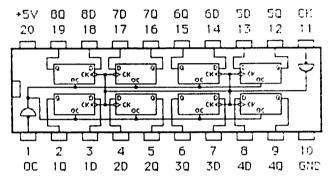

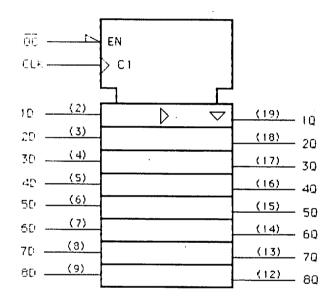

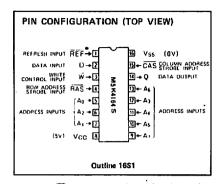

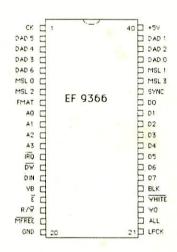

Man mißt, ob an allen IC-Sockeln die Versorgungsspannung von +5V ankommt. Dabei liegt bei Standard-TTL-Bausteinen jeweils am letzten Pin einer Fassung (z.B. bei 14-poligen an Pin 14, bei 16-poligen an Pin 16, bei 20-poligen an Pin 20), die Versorgungspannung von +5V. 0V bzw. Masse liegt jeweils auf dem letzten Pin der ersten Reihe (bei 14-poligen auf Pin 7, bei 16-poligen auf Pin 8, bei 20-poligen auf Pin 10). Achtung!: Bei den RAM-Bausteinen sind die Plus- und Masse-Anschlüsse genau andersrum (+5V liegt an Pin 8 und GND liegt an Pin 16). Beim Graphik-Prozessor EF 9366 liegt Masse auf Pin 20 und +5V auf Pin 40 (siehe auch Kapitel 9).

Liegt die Versorgungsspannung +5V und 0V (Masse,GND) an den richtigen Pins an, dann können die IC's eingesetzt werden. Dabei muß auf die Richtung der IC's geachtet werden. Die Markierung auf dem IC muß mit der Kerbe in der Fassung übereinstimmen.

#### 5.2 Test der GDP64HS im System

#### 5.2.1 Bestücken der ICs und erste Tests beim Komplettbausatz

Sie können jetzt alle ICs einstecken. Bitte achten Sie darauf, daß Sie die ICs richtig herum einstecken. Die Kerbe auf dem IC muß mit der Kerbe am Sockel bzw. auf dem Bestückungsdruck übereinstimmen. Kontrollieren Sie lieber doppelt, denn wenn ein IC falsch herum eingesteckt ist, ist es garantiert 'tot'.

Haben Sie ein Osszilloskop und wollen die Baugruppe Schritt für Schritt testen, so können Sie auch nach folgender Beschreibung vorgehen:

Zuerst wird nur das IC Jll eingesteckt (IC zur Takterzeugung). Wird die Leiterplatte nun auf den Bus gesteckt, muß an Jll/8 eine Taktfrequenz von 14 MHz zu messen sein.

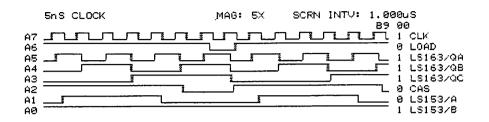

Wenn dieser Takt anliegt können die restlichen IC's bis auf den EF 9366 (J28) und die Speicherbausteine J16..J23 hineingesteckt werden; aber nicht bei angelegter Spannung!!! Wird danach die Spannung wieder angelegt, muß an IC J28/1 ein 1,75 MHz Signal messbar sein. An J7 müssen folgende Signale zu messen sein:

Bild 8

Anschließend muß die Versorgungsspannung wieder weggenommen und der EF 9366 eingesteckt werden. Einschalten der Spannung muß auf dem Monitor ein abgegrenzdunkles Bild erkennbar sein. Es ist noch keine Bildinformation erkennbar (auch nicht vorhanden). Synchronsignal, das der EF 9366 erzeugt, muß mit dem Oszilloskop am BAS - Ausgang zu messen sein. Wie das Signal aussieht, ist in Kapitel 3 unter 'Daten- übertragung zum Monitor' zu sehen.

Anschließend sollte die Spannungsversorgung der Speicherbausteine J16..J23 kontrolliert werden. Jeweils an Pin 8 müssen 5 Volt anliegen (Masse liegt an Pin 16). Nach Abschalten der Spannung können die Speicherbausteine eingesteckt werden.

#### 5.2.2 Bestücken der ICs und erste Tests beim Aufbausatz

Da die Ausstattung des Aufbausatzes auf die Weiterverwendung von ICs der 'alten' GDP64k abgestimmt ist, sollten Sie diese กแก bereithalten. Beim Entnehmen der benötigten Schaltkreise benützen Sie bitte einen Schraubendreher der Grösse zwei oder drei, bzw. ein Taschenmesser mit schmaler Klinge. Das Werkzeug wird nun vorsichtig von der Stirnseite her in den Spalt zwischen IC und ICs eingeschoben. Durch die Keilform des Schraubendrehers wird Schaltkreis jetzt im vorderen Bereich aus der Fassung Durch leichte Kippbewegungen angehoben. wird Schaltkreis vollständig ausgehebelt. Eventuell verbogene IC-Beinchen werden mit einer Flachzange geradegerichtet. Verwendung eines Taschenmessers können Sie ebenfalls Kippbewegungen durchführen, oder nachdem die Klinge ganz untergeschoben wurde das IC mit Drehbewegungen aus seiner Fassung lüften. Beachten Sie hierbei jedoch die CMOS- Warnung!

Beim Umsetzen der ICs arbeiten Sie sich bitte IC für IC durch, d.h. hier Entnehmen und dort Einsetzen.

Besondere Erwähnung verdienen die ICs J1 und J31 (6-fach Inverter 7405): Im Schaltplan und im Bestückungsplan der GDP64HS werden hierfür LS- Typen vorgesehen. Alternativ können anstatt der LS- Typen aber auch Standardtypen eingesetzt werden, die auf der GDP64k bereits vorhanden sind. Aus diesem Grund sind dem Aufbausatz diese Bausteine nicht beigelegt worden.

Die sonstige Vorgehensweise entspricht der Testamleitung unter Kapitel 5.2.1.

#### 5.2.3 Test im Z80-System

Sind nun alle Bausteine bestückt, kann der Test mit der Software beginnen. Setzen Sie in Ihrem Rechner nur das Grundprogramm ein, so reicht es, wenn Sie die SBC3 (bestückt mit EGRUND2), die KEY bzw. KEY2 und die GDP64HS im BUS stecken haben. Der Monitor wird mit dem Monitorkabel am Monitor und an BU1 der GDP64HS angeschlossen. Nach dem Einschalten der Spannung muß nach einer kurzen Copyright Meldung das Grundmenue des Grundprogrammes erscheinen. Bleibt das Bild dunkel, so sollten Sie erst mal am Kontrastregler des Monitors drehen. Es kann nämlich sein, daß dieser am Anschlag steht und somit kein Bild kommen erscheinen kann.

Haben Sie einen Z80-Rechner mit FLOMON, so genügt es für den ersten Test die SBC3 (mit FLOMON), die KEY bzw. KEY2, eine Speicherkarte mit mindestens 64k RAM (z.B. ROA64, RAM64, RAM256, ROA256/1M) und die GDP64HS einsetzen. Schließen Sie die Tastatur an die KEY und den Monitor an die GDP64HS an. Wenn Sie jetzt den Rechner einschalten, muß das FLOMON-Grundmenü erscheinen. Wenn dieses Menu nicht erscheint, können Sie natürlich noch kontrollieren, ob der Kontrastregler am Monitor richtig eingestellt ist. Bringt dies auch keinen Erfolg, sollten Sie mit Kapitel 6 fortfahren.

#### 5.2.3 Test im 680xx System

#### 5.2.3.1 Test im 68008 System

Zum Test der GDP64HS im 68008-System benötigen Sie als Mindestkonfiguration eine CPU68k, eine ROA64 (mit EASS 0-3 und mindestens einem RAM 8k; eingestellt auf Bank 0), eine KEY bzw. KEY2 und eine GDP64HS. Wenn Sie jetzt die Tastatur an der KEY und den Monitor an der GDP64HS anschließen, und die Spannung einschalten, erscheint nach einer kurzen Copyright Meldung das Grundmenue des Grundprogrammes 68k. Sollte es nicht erscheinen, können Sie wiederum versuchen den Kontrastregler des Monitors richtig einzustellen. Bringt dies keinen Erfolg sollten sie mit Kapitel 6 fortfahren.

#### 5.2.3.2 Test im 68000-System

Zum Test der GDP64HS im 68000 System benötigen sie folgende Mindestkonfiguration: Eine CPU68000, zwei ROA64k (mit EG68000 ODD und EVEN; auf Bank 0 eingestellt), eine KEY bzw.KEY2 und die GDP64HS. Dabei ist zu beachten, daß eine ROA64 auf der "ODD"-Seite (ungerade) der CPU68000 steckt, und die andere auf ROA, die KEY und die GDP64HS auf der "EVEN" Seite gesteckt sein muß (siehe auch CPU68000 Handbuch Seite 5 unten). Nachdem Sie die Tastatur (an die KEY) und den Monitor (an die GDP64HS an BU1) angeschlossen haben, können Sie den Rechner einschalten. Es muß muß das Grundmenü des Grundprogrammes erscheinen. Bleibt der Bildschirm dunkel, sollten Sie den Kontrastregler des Monitors noch einstellen; dieser könnte am Anschlag sein und daher kein Bild zeigen. Bleibt auch dies ohne Erfolg, können Sie mit Kapitel 6 fortfahren.

#### 5.2.3.3 Test im 68020-System

Zum Test der GDP64HS im 68020 System benötigen Sie folgende Mindestkonfiguration: CPU68020, vier ROA64k mit EG68020 auf Bank 0 eingestellt, eine KEY bzw. KEY2 und die GDP64HS. Auch bei dieser Konfiguration sollten Sie darauf achten, daß Sie die Baugruppen an die richtige Stelle im Bezug auf die CPU68020 stecken (siehe hierzu im CPU68020 Handbuch Seite B). Wenn Sie jetzt die Tastatur (an die KEY) und den Monitor an die GDP64HS (an BUI) anschließen, muß das Grundmenu des Grundprogrammes 68k auf dem Bildschirm erscheinen. Sollte kein Bild erscheinen, sollten Sie den Kontrastregler des Monitor noch einstellen; ist dieser nämlich am Anschlag kann kein Bild erscheinen. Bringt dies aber auch nicht den erhofften Erfolg sollten Sie mit Kapitel 6 fortfahren.

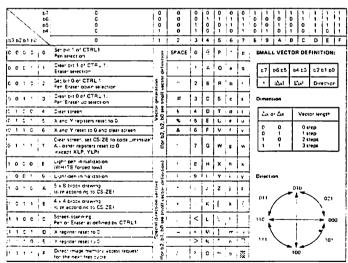

#### 5.3 Beispiel und Testprogramme:

#### Beschreibung zu den Testprogrammen:

#### 1. Beispiel: (Buchstaben) (lauffähig ohne Flomon)

Ist das Bit 2 des Registers 70h auf 0, so darf kein Kommando an die GDP gegeben werden, da diese dann beschäftigt ist. Man muß also vor jeder Befehlsausgabe oder jedem Umsetzen eines der anderen Register darauf warten, daß dieses Bit auf eins liegt. (Siehe auch 'Warteschleife' wail ). Im Programm: Aufruf der Warteschleife durch 'call wail'.

Wird der Wert 6 an die GDP geleitet, so erfolgt 'Bildschirm Löschen' und es kann die Ausgabe beginnen. Zuerst wird der Buchstabe 'A' in gewohnter Größe geschrieben. Ofh an 73h bewirkt 'Groß -Schreibung'.Das Zeichen 'B' wird groß auf dem Bildschirm dargestellt. Danach wird wieder auf Kleinschreibung umgestellt (11h nach 73h), und es wird der Buchstabe 'C' geschrieben.

Die Verzögerung gestattet es, das Bild eine Weile anzusehen, bevor wieder ins Betriebssystem zurückgesprungen wird.

#### 2. Beispiel: (Figurenzeichnen mit FLOMON)

Dieses Programm zeigt das Zeichnen verschiedener Figuren auf dem Bildschirm.

Mit dem Befehl 'ld de,Al' wird die unter 'Al' stehende Information eingelesen und mit 'call string' zur Ausführung gebracht.

Mit der Routine 'Eingabe' wird auf einen Tastendruck gewartet. Was die einzelnen Zeichen hinter db.. bedeuten ist dem Programm zu entnehmen.

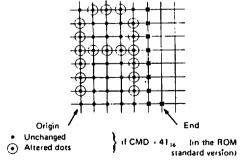

#### 3. Beispiel: (Vektoren mit FLOMON)

Das dritte Beispiel zeigt die Darstellung von Vektoren, die zu einem sternähnlichen Gebilde zusammengefügt werden. Die Befehle 'clrall' und 'wait' sind FLOMON- Befehle ;ihre Sprungadressen werden am Programm Anfang definiert. 'clrall' löscht alle Bildschirmseiten und 'wait' führt genau das aus, was im vorigen Beispiel in der 'wail' Routine stand. Zunächst werden die X und Y Register geladen (=Anfangspunkt Bildschirmmitte), der Schreibstift gesetzt (PEN down), und die Richtung, in der gezeichnet werden soll, festgelegt. Das Ganze wird in der Schleife 'LOOP' abgearbeitet, die

durch incrementieren von b die Zeichenrichtung ändert.

|                                                             |                                                            |                          |                                                                         | **************************************                                                                                            |

|-------------------------------------------------------------|------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 0070<br>0060                                                |                                                            | gdp<br>seite             | equ 70h<br>equ 60h<br>org 8800h                                         | :BASIS<br>;Seltenadr.                                                                                                             |

| 8800'<br>8802'<br>8804'<br>8807'<br>8809'                   | 3E FO<br>D3 60<br>CD 8839 '<br>3E 06<br>D3 70              | start:                   | ld a,0F0h out (seite),a call wail ld a,6 out (gdp),a                    | ;Seite 3 verwenden<br>;warten bis GDP fertig<br>;Warteschleife aufrufen<br>;Bildschirm löschen<br>;und ausführen                  |

| 880B'<br>880E'<br>8810'<br>8812'<br>8814'                   | CD 8839 ' 3E 03   03 71   3E 41   03 70                    |                          | call wai1 ld a,3 out (gdp+1),a ld a,41h out (gdp),a                     | ;Warteschleife aufrufen<br>;PEN down<br>;PEN-Mode<br>;Zeichen A laden<br>;und ausgeben                                            |

| 8816'<br>8819'<br>8818'<br>8810'<br>881F'                   | CD 8839 ' 3E 0F D3 73 3E 42 D3 70                          |                          | call wail ld a,15 out (gdp+3),a ld a,42h out (gdp),a                    | :Warteschleife aufrufen<br>:* 15 (Zeichen gross)<br>;Zeichen 8 laden<br>;und ausgeben                                             |

| 8821'<br>8824'<br>8826'<br>8828'<br>8828'                   | CD 8839 ° 3E 11 D3 73 3E 43 D3 70                          |                          | call wail ld a,11H out (gdp+3),a ld a,43h out (gdp),a                   | ;Warteschleife aufrufen<br>;* 1 (Zeichen klein)<br>;Zeichen C laden<br>;und ausgeben                                              |

| 882C'<br>882F'<br>8830'<br>8832'<br>8833'<br>8836'<br>8836' | 01 2222<br>0B<br>16 FF<br>15<br>20 FD<br>78<br>B1<br>20 F6 | ; Verzögerung<br>wschl:  | ld bc,2222h dec bc ld d,0ffh er: dec d jr nz,er ld a,b or c jr nz,wschl | ;z.B. 2222 mal durchlaufen<br>;Schleifenanfang<br>;innere Schleife<br>;durch diese Befehle wird<br>;das Flag Register beeinflusst |

| 8839'<br>8838'<br>8830'<br>883F'                            | DB 70<br>E6 04<br>28 FA<br>C9                              | ; Warteschleifd<br>wail: | _                                                                       | ;Warten bis GDP fertig<br>;(Maskierung)<br>;erst wenn fertig<br>;dann nächsten Befehl                                             |

|        |             | . Z80                                   |                            |

|--------|-------------|-----------------------------------------|----------------------------|

|        |             | , ************************************* | ********                   |

|        |             | :* ZEICHENPROGRAMM ra                   | ku 3'87 *                  |

|        |             | *********                               | ********                   |

| 000D   |             | cr equ Odh                              | ;Return-Taste              |

| 0060   |             | seite egu 60h                           | ;Seitenadresse             |

| 0005   |             | system equ 00005h                       | ;Systemadresse             |

| 0024   |             | stop equ '\$'                           | :Ende Eingabeliste         |

|        |             | org 8800h                               |                            |

| 88001  | AF          | start: xor a                            | :Hier wird Seite O         |

| 8801'  | D3 60       | out (seite),a                           | ;verwendet                 |

| 8803   | 11 8820'    | ld de.al                                | ;Einlesen der Liste        |

| 8806'  | CD 880C'    | call string                             | ;ausführen                 |

| 8809'  | C3 8812'    | jp eingabe                              | ;UP Eingabe rufen          |

| 880C ' | OE 09       | string: 1d c,9h                         | ;Zeichenstring zur         |

| 880E ' | CD 0005     | call system                             | :Ausführung bringen        |

| 8811'  | C9          | ret                                     |                            |

| 8812'  | 3E FF       | eingabe:1d a,Offh                       | ;Warten bis                |

| 88141  | 5F          | ld e,a                                  | ;eine Taste                |

| 8815'  | 0E 06       | ld c,6h                                 | ;gedrückt wird             |

| 8817'  | CD 0005     | call system                             |                            |

| 881A1  | FE 00       | cp Oh                                   |                            |

| 881C ' | CA 8812'    | jp z.eingabe                            |                            |

| 881F'  | C9          | ret                                     |                            |

| 88201  | 18 18 47 0D | al: db lbh,lbh,'G',cr                   | ;Zeichenliste (Grafikmodus |

| 88241  | 5A OD       | db 'Z',cr                               | ;Bildschirm löschen        |

| 88261  | 4D 20 31 30 | db 'M 100 100',cr                       | ;Anfangspunkt setzen       |

| 882A1  | 30 20 31 30 |                                         |                            |

| 882E 1 | 30 OD       |                                         |                            |

| 8830'  | 52 20 35 30 | db 'R 50 50',cr                         | ;Rechteck zeichnen         |

| 88341  | 20 35 30 CD |                                         |                            |

| 88381  | 4F 20 33 30 | db '0 30 30 0 360',cr                   | :Kreis zeichnen            |

| 8830'  | 20 33 30 20 |                                         |                            |

| 8840'  | 30 20 33 36 |                                         |                            |

| 8844   | 30 OD       |                                         |                            |

| 88461  | 42 20 48 61 | db 'B Hallo',cr                         | ;'Hallo` schreiben         |

| 884A1  | 6C 6C 6F 0D |                                         |                            |

| 884E'  | 58 20 30 0D | db 'X O',cr                             | ;Rücksprung                |

| 88521  | 41 24       | db 'A',stop                             | zum Alpha-Modus            |

|        |             | END                                     |                            |

|                |         | . z80        |         |            |                 |                           |

|----------------|---------|--------------|---------|------------|-----------------|---------------------------|

|                |         | ;*****<br>;* | Demopro | orann V    | ectoren         | raku 3'87 *               |

|                |         | *****        | *****   | ****       | *****           | ******                    |

| 0070           |         |              | gdp     | equ        | 70h             | ;BASIS                    |

| 0060           |         |              | seite   | equ        | 60h             | ;Seitenadr.               |

| F040           |         |              | clrall  |            | 0f040h          | :Bildschirmseiten löschen |

| F055           |         |              | wait    | equ        | 0f055h          | :Warten                   |

| 0005           |         |              | system  | equ<br>org | 00005h<br>0100h | ;Systemadresse            |

| 0100'          | CD F040 | start:       | call cl | rall       |                 |                           |

| 0103'          | CD F055 |              | call wa | iit        |                 |                           |

| 0106'          | 3E 10   |              | 1d a,01 |            |                 | ;Hier wird Seite 1        |

| 0108'          | D3 60   |              | out (se | eite),a    |                 | ;verwendet                |

| 010A'          | 06 17   |              | ld b,23 |            |                 |                           |

| 0100'          | 0E 20   |              | loop:   | •          |                 |                           |

| 010E'<br>010E' | CD F055 |              | roop.   | call w     | ait             |                           |

| 0111'          | 3E 05   |              |         | ld a,5     |                 |                           |

| 0113'          | D3 70   |              |         | out (g     |                 |                           |

| 0115'          | CD F055 |              |         | call w     | ait             | :Warteschleife aufrufen   |

| 0118'          | 3E 7E   |              |         | 1d a,0     | 7eh             | ;Y-Register low           |

| 011A'          | D3 7B   |              |         | out (g     | dp+11),a        |                           |

| 0110'          | CD F055 |              |         | call w     |                 | ;Warteschleife aufrufen   |

| 011F'          | 3E FF   |              |         | ld a,0     |                 | ;X-Register low           |

| 0121'          | D3 79   |              |         | out (g     | dp+09),a        |                           |

| 0123'          | CD F055 |              |         | call w     |                 |                           |

| 0126           | 3E 03   |              |         | ld a,3     |                 | ;pen down                 |

| 0128'          | D3 71   |              |         | out (gd    | p+1).a          |                           |

| 012A'          | CD F055 |              |         | call w     |                 | ;Warteschleife aufrufen   |

| 0120'          | 78      |              |         | ld a,b     |                 | :Richtung festlegen       |

| 012E'          | D3 70   |              |         | out (g     | dp),a           |                           |

| 0130'          | CD F055 |              |         | call w     |                 | ;Warteschleife aufrufen   |

| 0133'          | 3E 45   |              |         | 1d a,4     |                 | ;laenge X-Richtung        |

| 0135'          | D3 75   |              |         | out (g     | dp+5),a         |                           |

| 0137           | CD F055 |              |         | call w     |                 | -laongo V Dichtung        |

| 013A'          | 3E 50   |              |         | ld a,5     |                 | ;laenge Y-Richtung        |

| 013C'          | D3 77   |              |         | out (g     | dp+7),a         |                           |

| 013E.          | 04      |              |         | inc b      |                 |                           |

| 013F'          | 78      |              |         | ld a,b     | )               |                           |

| 0140'          | 91      |              |         | sub c      |                 |                           |

| 0141'          | 20 CB   |              |         | jr nz,     | 100p            |                           |

```

0143' 3E FF eingabe:ld a,0ffh

0145' 5F ld e,a

0146' 0E 06 ld c,6h

0148' CD 0005 call system

014B' FE 00 cp 0h

014D' CA 0143' jp z,eingabe

```

END

Zum Schluß hier noch ein kleines Programm, welches auf 680xx-Systemen läuft:

In diesem Beispiel wird von den Befehlen 'hebe', 'senke', 'drehe' und 'schreite' Gebrauch gemacht.

Zuerst wird die Schildkröte bei x = 50, y = 50 positioniert, Richtung nach oben. Dann schreitet sie 50 mal schreibend nach oben, hebt an, schreitet 50 mal ohne zu schreiben, wird gedreht und schreibt weiter.

```

;*

Demo- Programm (Schildkroete)

fuer 680xx- Systeme

***************

;setzen bei 50/50

move #50,d1

move #50,d2

move #90.d3

;Richtung nach oben

jsr §set

;50 * schreiten und zeichnen

move #100,d0

jsr §schreite

;Schreibstift anheben

isr Shebe

move #50,d0

;50 * schreiten und zeichnen

jsr §schreite

move \#-45,d0

;um 45 Grad drehen

isr §drehe

;Schreibstift absenken

jsr §senke

move #50,d0

;50 * schreiten und zeichnen

isr §schreite

move \#-45,d0

;um 45 Grad drehen

jsr §drehe

;50 * schreiten und zeichnen

move #50,d0

jsr §schreite

rts

```

#### 5.4 Jumperung der Baugruppe

Auf der Baugruppe sind die Jumper JMP1 bis JMP5. Alle diese Jumper sind voreingestellt und müssen bei Standardkonfigurationen auch nicht geändert werden. Hier nun die Beschreibung der einzelnen Jumper:

JMP1: Damit wird in Verbindung mit JMP2 und JMP3 auf den Betrieb mit dem EF 9367 umgestellt. Dabei ist jedoch der 14 MHz- Quarz gegen einen 12MHz- Quarz auszuwechseln.

In der voreingestellten Position von JMP1 wird der EF 9366 bedient.

Beim Einsatz des Videoprozessors EF 9367 ist eine Hardcopy- Funktion bis auf weiteres nicht möglich.

JMP2: JMP2 dient zur Umstellung der Auflösung der GDP64HS.

Die Standardauflösung liegt bei 256 x 512

Bildpunkten. Legt man diesen Jumper um, kann man auch

mit einer Auflösung von 512 x 512 Bildpunkten im

Interlace-Modus (Zeilensprungverfahren) arbeiten.

Allerdings kann dies nur mit dem Graphikprozessor

9367 durchgeführt werden. Außerdem gibt es für diese

Auflösung eigentlich keine Software, da das Flimmern

des Interlace Modus wohl meistens als störend

empfunden wird.

JMP3 dient nur dazu einzustellen, welcher Graphikprozessor verwendet wird (9366 oder 9367). Voreingestellt ist der 9366.

JMP4: JMP4 ist in drei Abschnitte aufgeteilt. Die oberen 2 Brücken dienen zum Invertieren des Videosignales. Die Brücken 3 und 4 dienen zum Invertieren des HSync-Signales und die Brücken 6 und 7 zum Invertieren des Vsync-Signales.

JMP4 0 1 0 0 2 0 0 3 0 0 4 0 0 5 0 0 6 0

Videosignal invertiert: 1 gebrückt, 2 offen Videosignal nicht invertiert: 2 gebrückt, 1 offen HSYNC invertiert: 3 gebrückt, 4 offen HSYNC nicht invertiert: 4 gebrückt, 3 offen VSYNC invertiert: 5 gebrückt, 6 offen VSYNC nicht invertiert: 6 gebrückt, 5 offen

JMP5: JMP5 dient lediglich dazu, das VSYNC-Signal auf den INT zu legen. Dieser JMP ist natürlich offen.

JMP5 wurde vorgesehen, um einen definierten Interrupt von 20 ms erzeugen zu können. Dies ist eventuell für Multitasking-Aufgaben interessant. Sonst bleibt dieser Jumper immer offen.

#### 6. Fehlersuchanleitung

Sollte Ihre Baugruppe bei den in Kapitel 5 beschriebenen Tests nicht funktionieren, so heißt es jetzt systematisch auf Fehlersuche zu gehen.

Wir wollen Ihnen nun ein paar Vorschläge machen, wie eine systematische Fehlersuche mit und ohne Oszilloskop vor sich gehen kann:

#### 6.1 Mögliche Fehler und ihre Behebung

- 6.1.1 Sind die bisher verwendeten Baugruppen in Ordnung? (Funktionierte das System ohne die Baugruppe GDP 64K?)

- 6.1.2 Sind die Jumper richtig gesteckt?

- 6.1.3 Machen Sie zuerst eine Sichtprobe. Können Sie irgendwo auf Leiterplatte unsaubere Lötstellen (zuviel Lötzinn, manch- mal zieht das Lötzinn Fäden) erkennen, die eventuell einen Kurzschluß verursachen könnten? Dann müssen Sie diese Lötstellen nachlöten und die unzulässige Verbindung beseitigen.

- 6.1.4 Haben Sie auch alle IC's richtig herum und am richtigen Platz eingesteckt? (Vergleiche mit Bestückungsplan)

- 6.1.5 Sind alle gepolten Bauteile (Elkos, Dioden, usw.) richtig herum eingelötet?

- 6.1.6 Haben Sie auch keine Lötstelle vergessen zu löten? (sehen Sie lieber noch einmal nach)

- 6.1.7 Sehen Sie irgendwo "kalte" Lötstellen? Kalte Lötstellen erkennt man daran, daß sie nicht glänzen, sie sind im Vergleich mit richtig gelöteten Lötstellen trübe.

- 6.1.8 Haben Sie auch nicht zu heiß gelötet? Wenn der Lötkolben zu heiß eingestellt ist und (oder) Sie zu lange auf der Lötstelle bleiben, dann kann es passieren, daß sich die Leiterbahnen von der Platine lösen und Unterbrechungen bilden. Ferner kann es auch passieren, daß Durchkontaktierungen unterbrochen werden, oder daß Bauteile durch zu heißes Löten zerstört werden.

- 6.1.9 Nehmen Sie alle IC's aus ihren Fassungen. Schauen Sie sich beim herausnehmen die IC-Füßchen genau an. Manchmal sind Füßchen umgeknickt oder steckten daneben. Nehmen Sie sich die Layouts zur Hand und kontrollieren Sie alle Leiterbahnen, mit einem Durchgangsprüfer oder mit einem Ohmmeter auf Durchgang. Bereits kontrollierte Leiterbahnen können Sie, der Übersicht wegen, auf dem Layout mit Bleistift durchstreichen oder mit Farbstiften nachziehen.

6.1.10 Prüfen Sie die Versorgungsspannung mit einem DigitalVoltmeter (am Bus +5V, nicht am Netzgerät, da am

Kabel bei starker Belastung bis zu 0,5V abfallen

können). Toleranzen von +/- 5% also von 4,75V bis

5,25V sind erlaubt. Falls die Spannung zu gering ist,

prüfen Sie, ob die Verbindung vom Netzteil zum

Bus mit ausreichend dickem (mind. 2 mm Quadrat)

Kabel erfolgt ist. Gegebenenfalls müssen Sie Ihr

Netzteil nachregeln. Vorsicht: nie über 5,1V

nachregeln, da sich auf einigen Platinen 5,1V

Zenerdioden befinden, die ab 5,1V durchschalten, was

entweder zum Zusammenbruch Ihrer Versorgungsspannung

führt oder die Zenerdiode bis zu Ihrer Zerstörung

erhitzt.

Übrigens: Wir empfehlen 5,05V.

Wenn Sie alle Leiterbahnen kontrolliert und nichts gefunden haben, dann ist die Wahrscheinlichkeit groß, daß ein Bauteil defekt ist.

Wenn Sie einen Prüfstift oder ein Oszilloskop haben, dann können Sie jetzt überprüfen, ob an den jeweiligen Ausgängen die richtigen Signale anliegen. Welche Signale wo anliegen müssen, können Sie aus der Schaltungsbeschreibung und aus dem Schaltplan entnehmen.

Falls Sie keine Meßgeräte haben, dann müssen Sie alle Bauteile systematisch austauschen, bis Sie das Defekte gefunden haben. Verwenden Sie dazu eventuell eine zweite Baugruppe (die eines Freundes oder eines Bekannten).

Sollten Sie gar nicht zurande kommen, hilft Ihnen unser Pauschal-Reparatur-Service, dessen Bedingungen Sie der Preisliste entnehmen können.

#### 7. Schaltungsbeschreibung

#### 7.1 Wie funktioniert die Baugruppe?

Das Herz der GDP64HS ist der Graphik Display Prozessor EF 9366 für 512 mal 256 Bildpunkte. Es könnte aber auch der EF 9365 oder der EF 9367 verwendet werden, dazu müssen aber die Brücken JMP1, JMP2 und JMP3 verändert werden. Standard ist die Bestückung mit dem EF 9366, auf den auch die gesamte Software abgestimmt ist.

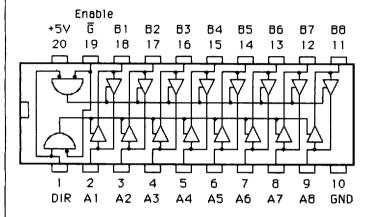

Der GDP J28 ist an den Datenbus und an die Adressbits A0...A3 angeschlossen. Die vier Adressbits bewirken, daß eines der 16 GDP-Register ausgewählt wird. Über den Datenbus kann dann in das gewählte Register geschrieben bzw. vom gewählten Register gelesen werden. Der Datenbus des Graphikprozessors ist außerdem noch durch einen biderektionalen Treiber (J27) vom Systemdatenbus getrennt, der nur dann aktiviert wird, (J27/19) wenn auf ein Register des GDP zugegriffen wird (Portadressen 70h bis 7Fh). Die Richtung des Datentransfers wird durch das READ-Signal festgelegt (J27/1).

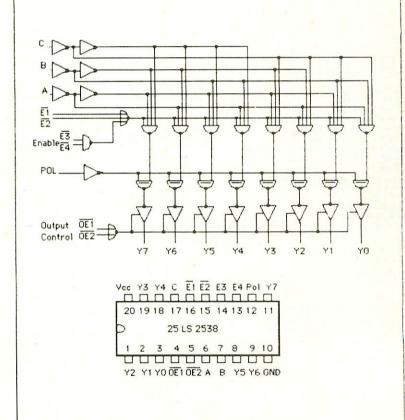

Die Ausdekodierung der Adressen 70h bis 7Fh übernimmt der 3 zu 8 Dekoder (J30). Wird eine Portadresse 70h bis 7Fh angesprochen, so wird der Ausgang 7 (J30/7) aktiviert (low). Dieser Ausgang steuert die Enable-Eingänge des Graphikprozessors (J28/17) und des bidirektionalen Treibers (J27/19).

Die Ausdekodierung der Adressen 60h und 61h übernimmt zum Teil auch der 3 zu 8 Dekoder 74LS138. Der Ausgang Y6 (J30/9) wird aktiviert, wenn eine Adresse von 60h bis 6Fh angesprochen wird. Die Selektion der Adressen 60h und 61h aus diesen 16 Portadressen übernimmt der zweite 3 zu 8 Dekoder (J29). An dessen Ausgang Y0 (J29/15) liegt dann ein Low-Signal an, wenn auf Port 60h zugegriffen wird. Der Ausgang Y1 (J29/14) wird aktiv (LOW), wenn auf Port 61 zugegriffen wird. Soll z.B auf Port 60 (Seiten- und RMW-Port) geschrieben werden, so wird der Ausgang J29/15 low, ebenso ist das Signal -WR LOW. Dadurch wird der Ausgang des ODER J3/8 low, was das Latch J24 dazu bewegt neue Daten aufzunehmen. Mit dem Inhalt dieses Latches kann die Schreib- und Lesseite eingestellt, sowie das Steuerbit für RMW gesetzt werden (siehe Abb.).

| 1 | 7 | ! | 6     | ! | 5 | ! | 4 | !   | 3   | !   | 2   | 1   | 1   | 1  | 0     | ! |

|---|---|---|-------|---|---|---|---|-----|-----|-----|-----|-----|-----|----|-------|---|

|   |   |   | <br>! |   |   |   |   |     |     |     |     |     |     |    | <br>! |   |

|   | 1 |   | 1     |   | ! |   | ! |     |     |     |     | RM  | W   |    |       |   |

|   | ! |   | 1     |   | ! |   | 1 |     |     |     |     |     |     |    |       |   |

|   | 1 |   | 1     |   | ! |   | ! |     |     |     |     |     |     |    |       |   |

|   | İ |   | 1     |   |   |   |   | - I | ese | sei | te  | 0 b | is  | 3  |       |   |

|   | 1 |   | 1     |   |   |   |   |     |     |     |     |     |     |    |       |   |

|   |   |   |       |   |   |   |   | - S | chr | eib | sei | te  | 0 b | is | 3     |   |

RMW: Bit 0 = LOW RMW nicht aktiviert

Bit 0 = HIGH RMW aktiviert

Die Schreib- und Leseseite kann universell eingestellt wer-

den. Man kann z.B. im Hintergrund schreiben, also Lese- und Schreibseite verschieden wählen, oder man kann die Seiten wechselseitig hin und herschalten, um zwei Seiten qasi gleichzeitig sichtbar zu haben. Die Seiten können synchron (nach einem VSYNC-Signal) oder asynchron (zu einem beliebigen Zeitpunkt umgeschalten werden.

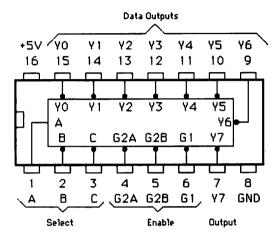

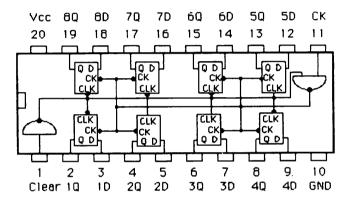

Damit es hierbei nicht zu Kollisionen kommen kann, dient J12, ein 2 mal 4 zu 1 Multiplexer, als Umschalter für die

Videospeicherseiten (je 16kB).

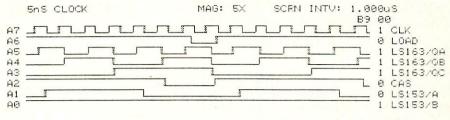

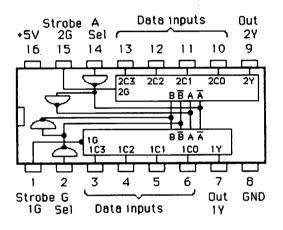

Zunächst sei die Brücke (Jumper) JMP2 auf der Stellung '9366' (Ist auf der Platine bereits realisiert). Damit ist nur der obere Teil des Multiplexers (J12) maßgebend. J12 erzeugt mit seinen Ausgang 1Y (J12/7) das jeweils höchstwertige Adressbit Al5 bzw. A7 der gemultiplexten Adresse, deren Wertigkeiten von der gewählten Seite abhängig sind. Abhängig von der Information an den Select- Eingängen A und B (J12/14,2) wird einer der Eingänge 1CO...1C3 (J12/6,5,4,3) auf den Ausgang 1Y (J12/7) durchgeschaltet. Die logischen Pegel an den Eingängen 1CO und 1C1 (J12/6,5) bestimmen die Seite, aus der gelesen werden soll, 1C2 und 1C3 (J6/4,3) definieren die Schreibseite (vgl. auch obige Abbildung). Die Taktaufbereitungslogig (J8 und J7) sorgt dafür, daß die Adressbits im für die Speicher richtigen Timing erzeugt werden.

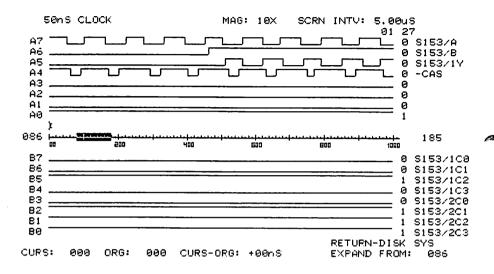

Bild 9 zeigt beispielsweise folgende Betriebsart: Auf Seite 1 einschreiben und die Seite 0 auslesen. Die Signale S153/1C0 und S153/1C1 liegen auf low (entspricht Seite 0). Das Signal S153/1C2 liegt auf high und S153/1C3 liegt auf

low, somit ist Seite 1 zum Beschreiben angewählt.

In der ersten Hälfte des Timingdiagrammes ist BLK (Signal S153/B) aktiv, d.h. der EF9366 ist mit der Bildausgabe aus Speicherseite O beschäftigt. Das Signal S153/1Y repräsentiert die Adressleitungen Al5 bzw. A7, jenachdem ob eine Spaltenadresse oder eine Zeilenadresse ausgegeben wird.

Al5 bzw.A7 sind hierbei erwartungsgemäß low.

In der zweiten Hälfte des Timingdiagrammes (Bild 9) ist die Leitung BLK (Signal S153/B) unwahr geworden; es wird in die DRAMs eingeschrieben. Man erkennt, daß Signal S153/IY seine Polarität wechselt: Wenn die fallende Flanke von RAS auftrit (geschieht ca. 150ns vor CAS, das sind rund 100% der Zeitdauer von CAS) ist Al5 low und bei CAS ist A7 high. A15 und A7 sind aber ja ein- und- dasselbe Signal (hier S153/IY). Signal RAS wurde hierbei nicht explizit aufgenommen, da es ja acht dieser Leitungen gibt.

#### NICOLET PARATRONICS

Bild 9

Seitenanwahl und Adressbiterzeugung. Zur Zeitintervallabschätzung: Der Beobachtungszeitraum beträgt 5us.

Wenn die RMW-Logik aktiviert wird, bewirkt sie eigentlich nichts anderes, als daß sie Dateneintragungen vom GDP aus in den Videospeicher abfängt, wenn es erforderlich ist modifiziert und schließlich in die vorgesehene Speicherstelle einschreibt. Dieser Ablauf ist natürlich sehr zeitkritisch, da während der Zeitdauer eines normalen Schreibzyklus zuerst noch gelesen und dann geschrieben wird.

RMW verändert also den Videospeicherinhalt, ohne daß es der GDP mitbekommt.

Dies ist dann nützlich, wenn z.B. auf ein zum Teil weißes Bild noch gezeichnet werden soll. Ohne RMW wird dann Weiß auf weiß gezeichnet, was dann natürlich unsichtbar ist. Mit RMW wird der Inhalt des Speichers erst einmal "angeschaut" (weiß oder schwarz) und dann entsprechend mit dem neuen Speicherinhalt modifiziert, d.h. wird auf einen hellen Hintergrund ein helles Rechteck gezeichnet, so erscheint dies mit RMW schwarz und ist damit sichtbar. Sehr nützlich ist dies z.B. für einen Maus-Zeiger, da dieser durch zweimaliges Zeichnen wieder verschwindet, ohne daß das Hintergrundbild zerstört wird.

Der Read-Modify-Write Vorgang kann in drei Schritten erläutert werden:

#### 1.READ

Will der GDP in eine Speicherzelle (1Bit) schreiben, wird die Leitung WE (Write Enable) am DRAM- Baustein kurzfristig "künstlich" auf high gehalten. Da jedoch die übrigen Signale wie Adressen, CAS und RAS stimmen, glaubt sich der betroffene DRAM- Baustein im Lese-Modus und gibt die gewünschte Bitinformation auf den internen Datenbus.

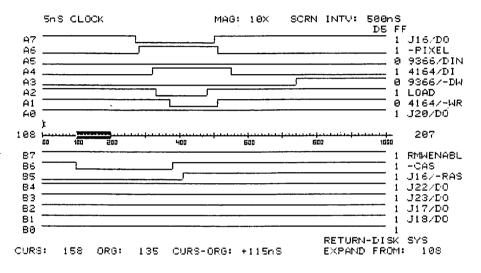

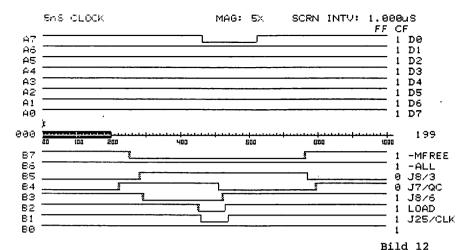

Im Timingdiagramm (Bild 10) ist zu erkennen:

RMW- Modus ist eingeschaltet (Signal RMWENABL ist high).

Der GDP 9366 leitet einen (vermeindlichen) WRITE-Zyklus ein (Signal 9366/-WR ist auf low und die Signale J16/-RAS und -CAS werden nacheinander low).

Der Baustein J16 befindet sich jedoch im Lesemodus (Signal 4164/-WR ist noch high) und gibt ein Bit aus (Signal J16/DO wird low). Die übrigen sieben DRAM-Bausteine sind nicht angesprochen, deren Datenausgänge sind hochohmig (Signale J20/DO, J22/DO, J23/DO, J17/DO und J18/DO sind high, da für Logik- Analysator tristate und high nicht unterscheidbar sind).

Die Wertigkeit (low) des Datenausgangsbit von J16 besagt, daß an dieser Stelle momentan ein heller Bildpunkt ist.

#### 2.MODIFY

Ist die Speicherinformation ausgelesen, wird sie nach folgendem Schema mit dem neuzuschreibenden Speicherinhalt verknüpft:

| altes Pixel                                                          | neues Pixel                                                          | tatsächliches Pixel                                                         |

|----------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------|

| hell (Bit =0)<br>hell (Bit =0)<br>dunkel (Bit =1)<br>dunkel (Bit =1) | hell (Bit =0)<br>dunkel (Bit =1)<br>hell (Bit =0)<br>dunkel (Bit =1) | <pre>dunkel (Bit =1) !! dunkel (Bit =1) hell (Bit =1) dunkel (Bit =1)</pre> |

(Pixel kommt von "picture element" und heißt: Bildpunkt, Bildelement.)

In Bild 10 ist zu erkennen, wie die Datenleitung, die zu den DRAM- Bausteinen führt (Signal 4164/DI), High- Potential annimmt. Das heißt, das tatsächliche Bildelement (Pixel) wird dunkel gezeichnet, obgleich der Prozessor 9366 ein helles Bildelement schreiben wollte (Signal 9366/DIN ist während der Beobachtungszeit low).

#### 3.WRITE

Das so behandelte Datenbit wird erst jetzt in die Speicherstelle eingetragen, indem die WR- Leitung low gezogen wird (Signal 4164/WR), noch bevor die Auswahl des Bausteins J16 beendet wird (-CAS und J16/-16 gehen wieder auf high). ist ein

Wenn die Signale CAS und RAS unwahr werden,

RMW- Zyklus abgeschlossen.

Bild 10

Timing eines RMW- Zyklus.

Zur Abschätzung der Zeitintervalle: Der gesamte dargstellte Zeitraum beträgt 500ns.

Schaltungstechnisch wurde dies mit nur wenigen Gattern realisiert. Da beim Schreiben auf der GDP64HS immer nur ein Bit geschrieben wird, ist auch immer nur einer der Speicherausgänge aktiv, die Ausgänge der anderen Speicher sind im hochohmigen Zustand. Dadurch können alle Speicherausgänge (siehe Bild 10, Signale J16/DO, J22/DO, J23/DO, J17/DO, J18/DO) auf ein Achtfach- NAND (J2/1,2,3,4,5,6,11,12) gelegt werden. Ist der Speicherausgang high (Bildpunkt dunkel), ist J2/8 invertiert, also auf high. Ist der der Ausgang Speicherausgang aber low, so ist der Ausgang J2/8 auch invertiert, also auf high (Bildpunkt hell) (siehe Bild 10, Signal -PIXEL). Das AND- Gatter (J5/9,10,8) dient lediglich dazu, den RMW zu sperren oder freizugeben. Ist das RMW-Bit gesetzt, geht das ausgelesene Bit weiter (zu J10/2), wenn nicht, wird es hier abgeblockt. Das ODER- Gatter (J10/1,2,3) vergleicht den ausgelesenen Speicherinhalt (durch J2 invertiert) mit dem einzuschreibenden Bit. War der ausgelesene Punkt hell (Low-Signal), liegt wegen der Invertierung an J2 ein High Signal an J10/2. Soll jetzt wieder ein heller Punkt geschrieben werden (also low), so wird der Ausgang J10/3 high und es wird ein dunkler Punkt in den Speicher geschrieben (siehe Bild 10, Signal4164/-WR).

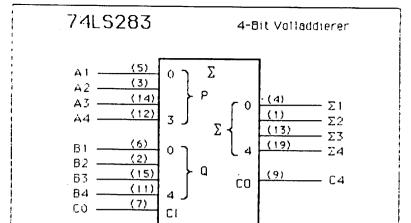

Die Verzögerung des Write-Signales für die DRAM- Speicher wird mit dem Load-Signal (J7/9) realisiert (siehe Bild 10, Signale LOAD und 4164/-WR). Mit J5/4,5,6 kann dieses Load-Signal mit Hilfe des RMW- Bits wieder gesperrt werden. Das OR-Gatter (J10/12,13,11) läßt ohne RMW das Schreibsignal DW (J28/14) original vom GDP passieren und mit RMW das Load-Signal .

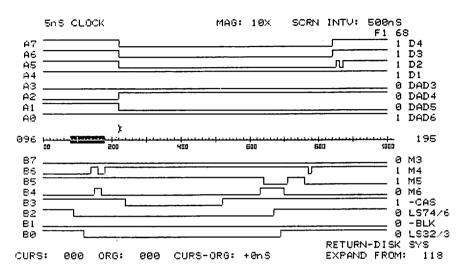

Wird auf den Port 61h geschrieben, so wird J29/14 aktiviert und gleichzeitg der Ausgang J3/6. Dadurch wird auf den Scroll-Port (J26) ein Byte übergeben. Der Wert dieses Bytes (von 0 bis 255) wird als "Scroll-Wert" zur horizontalen Adresse aufaddiert. Wird z.B. der Wert 40h auf Port 61h ausgegeben, so wird der Bildschirminhalt um 40h = 64 dezimal Punkte nach unten gescrollt. Der Rest, der unten vom Bildschirm verschwindet, wird oben wieder hineingeschoben (zyklisches Rotieren des Bildschirmspeichers). Der kleinste Wert, der beim Scrollen eine Wirkung zeigt, ist zwei, da die Datenleitung DO nicht an den Scrollport 61h angeschlossen ist. Steuerung des Hardscrolls wird von dem -BLK und dem Steuersignal für den Seitenport (J6/6) gesteuert. Diese beiden Signale werden ODER-verknüpft (J4/1/2/3) und ergeben ein vorgezogenes CAS- Signal für die Addierlogik. Addition der Scroll- Werte wird nur bei CAS durchgeführt, und außerdem nur im Display Modus, um den Schreibzugriff und den Refresh des Speichers nicht zu stören. In Bild 11 sind Signale LS74/6 und -BLK, die ODER- Verknüpft das Signal LS32/3 ergeben. Dieses verfrühte CAS- Signal aktiviert das Datenlatch ALS574 (J26/1); damit wird der Scrolloffset an die Addierer J14 und J15 angelegt. Mit dem Aktivieren des Latches J26 wird zugleich der Übertragseingang CI (Carry In) des niederwertigeren Addierers (J15/7) auf low gesetzt. Die Addition des Scrolloffsets zur horizotalen Adresse Bild 11 folgendermaßen nachzuvollziehen: Nachdem Signal LS32/3 aktiv wird (=low), liegen am Addierer J15 der niederwertigere Teil der Horizontaladresse (=90h) (Signale DAD3...DAD6) und der Offsetwert 02h (Signale D4..D1) an. DAD3 hat hierbei die höchste Wertigkeit und DAD6 die Niedrigste. Die Signale M3...M6 präsentieren das Ergebnis der Addition, nämlich 92h. Auch hierbei ist M3 höherwertiger als M6. fallenden Flanke von -CAS können nun die DRAM-Speicherbausteine die manipulierte Horizontaladresse übernehmen. Nachdem das Scrollen faktisch erledigt ist, wird der Latchbaustein J26 wieder hochohmig geschaltet (Signal LS32/3 wird high) und an den Eingängen der Addierer J14, J15 liegen High- Pegel an (Sicherheitshalber ist RN2 als Pull-Up- Widerstandsnetzwerk eingesetzt worden). Damit aber nicht OFFh zu jeder folgenden Adresse hinzugezählt wird, wird gleichzeitig der CI- Eingang des nieder-wertigeren Addierers (J15/7) mit High- Pegel beschaltet (0FFh + 01 = 00). Effektiv wird also zu den verikalen Adressen Null dazugezählt.

#### NICOLET PARATRONICS

Bild 11

Timingdiagramm beim Hardscroll.

Dargestellt sind die Signale rund um den Addierer J15 (Manipulation des niederwertigeren Teils der Horizontal-adresse).

Zum Abschätzen der Zeitintervalle: Der Beobachtungszeitraum erstreckt sich über 500ns.

Der Bildschirmspeicher kann über Port 60h rückgelesen werden. Dabei muß allerdings die Adresse des rückzulesenden Bytes im Bildschirmspeicher an das X- und Y-Register des Graphikprozessors übergeben werden und anschließend ins Kommandoregister der Befehl OFh eingetragen werden. Ist der Graphikprozessor im Display-Mode an der eingestellten Adresse angekommen, legt der Graphikprozessor das Signal MFREE auf low und beim nächsten Ladeimpuls (J7/9) wird der Datenwert ins Latch J25 übernommen. Dieses Byte muß nun über Port 60h eingelesen werden, bevor das Ganze wieder von neuem beginnt (Setzten der neuen Adresse, Befehl OFh ausgeben, warten bis Adresse im Display erreicht).

In Bild 12 wird beispielsweise der Wert FEh aus dem Videospeicher ausgelesen. Bevor dieses Bild aufgenommen werden konnte, wurde auf den dunklen Bildschirm an der Stelle x=256 und y=128 ein heller Punkt gezeichnet (Kurzvektor). Danach wurden die selben x- und y- Werte in die oben erwähnten xlsb- und ylsb- Register des EF9366 eingetragen. Normaler-