# SBC3

Die universelle CPU-Baugruppe mit der CPU Z80

für den NDR-Computer

Ausgabe 3

Graf Elektronik Systeme GmbH

Inhalt

7.

8.

9.

10.

11.

| 1. | Einführung                                                                                                                                                                                                                 |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2. | Technische Daten2                                                                                                                                                                                                          |

| 3. | Prinzipbeschreibung                                                                                                                                                                                                        |

| 4. | Aufbauanleitung .5 4.1 CMOS-Warnung .5 4.2 Stückliste .5 4.3 Bestückungsplan .7 4.4 Layout Bestückungsseite mit Bestückungsplan .7 4.5 Layout Bestückungsseite .8 4.6 Layout Lötseite .8 4.7 Aufbau Schritt für Schritt .9 |

| 5. | Testanleitung                                                                                                                                                                                                              |

| 6. | Fehlersuchanleitung                                                                                                                                                                                                        |

Die Zeitschrift LOOP ......72

Seite

#### 1. Einführung

#### 1.1 Zum NDR-Klein-Computer

Der NDR-Klein-Computer wird in der Fernsehserie "Mikroelektronik" - Mikroeomputer selbstgebaut und programmiert" aufgebaut, erklärt und in Betrieb genommen. Diese Serie wird vom Dorddeutschen Rundfunk, vom Sender Freies Berlin, vom Bayrischen Fernsehen und von Radio Bremen ausgestrahlt. Es werden bald auch die Regionalsender anderer Bundesländer die Sendung in ihr Programm aufnehmen. Zur Serie gibt es einige Begleitmaterialien, es ist daher nicht unbedingt notwendig, die Fernsehserie gesehen zu haben, um den NDR-Klein-Computer zu bauen und zu begreifen:

- Buch

Rolf-Dieter Klein,

"Rechner Modular"

Der NDR-Klein-Computer selbstgebaut und programmiert

ISBN 3-7723-8721-7, DM 68,erschienen im Franzis-Verlag, München

Auf diesem Buch baut die NDR-Serie auf

- Zeitschriften "mc" und "ELO" des Franzis-Verlages

- Zeitschrift "LOOP" der Firma Graf (siehe Kapitel 11.1)

- Videocassetten:

lizensierte Originalcassetten für den privaten Gebrauch. Auf diesen zwei Cassetten sind die 26 Folgen der Fernsehserie enthalten. Systeme: VHS, Beta, Video 2000 Preise: siehe gültige Preisliste

#### 1.2 Wozu dient die Baugruppe

Die Baugruppe SBC3 ist ein "Single Board Computer", d.h. soviel wie Einplatinencomputer. Ein "Einplatinencomputer" ist ein für sich allein funktionierender Computer, der nur noch diverse Ein/Ausgabe Einheiten fehlen um vernünftig arbeiten zu können. Auf dieser "SBC" sind CPU, Speicher und Schaltungen zur Steuerung der CPU vorhanden. Bei CP/M-Betrieb ersetzt die Baugruppe SBC3 die Baugruppen BANKBOOT und CPUZ80. Eine ROA64k oder RAM64/258 ist bei CP/M Betrieb schon noch nötig.

#### 1.3 Wie setzt man die Baugruppe SBC3 ein

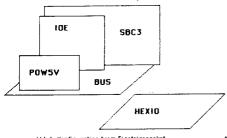

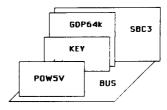

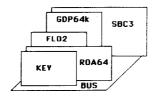

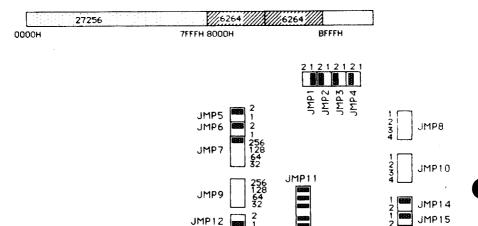

Da es sich um eine universelle CPU-Baugruppe handelt, kann die Baugruppe mit allen Baugruppen die für die CPU Z80 einsetzbar sind eingesetzt werden. Dies reicht vom Einsteigerpaket mit HEX-Tastatur bis zum Kommerziell einsetzbaren CP/M-Computer. Abb. 1 zeigt die Konfiguration beim Einsteigerpaket. Abb. 2 zeigt die SBC3 in einer Konfiguration mit Bildschirm und Tastatur, aber ohne Floppy-Laufwerke. Abb. 3 zeigt die Systemkonfiguration beim vollausgebauten CP/M-System (mit Floppy-Laufwerken und eventuell Festplatte).

Abb 1: Konfiguration beim Einsteigerpaket

Abb.2: Mögliche Konfiguration beim System ohne Floppy und ohne CP/M

Statt der ROA64k kann auch die dynamische Speicherkarte RAM64/256 verwendet werden. Als Stromversorgung wird das Netzgerät NE2 verwendet

Abb.3: Migliche Konfiguration beim System mit Floppy und CP/M

#### 2: Technische Daten

Baugruppengröße: 100 x 160 mm (Europakarte) Bus: NDR-Bus

Spannungsversorgung: +5V

Stromverbrauch: 500 mA

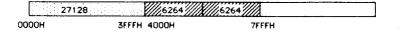

Durch default-Einstellung der JMP mögliche Speicher: 8k (2764, 6264)

Einsetzbare Speicher:EPROM: 4K (2732) max. 64k aber nur 32k 8K (2764) sind sinnvoll, da 16K (27128) sonst kein RAM 32K (27256)

> RAM: 2K (6116) max. 16k 8K (6264 bzw. 5565 usw.)

Akku: Spannung: +2,4V, Kapazität: 120 mAh ungefähre Haltedauer der RAM-Speicherinformation: 1 Jahr

BANK-Logik zur Adressierung von 1 MByte

Voll gepufferter Daten-, Adress- und Steuerbus

Taktversorgung: 4 (Z80A) und 8 MHz (Z80H)

Wait-Zyklen einstellbar getrennt für Speicher und I/O

#### 3. Prinzipbeschreibung

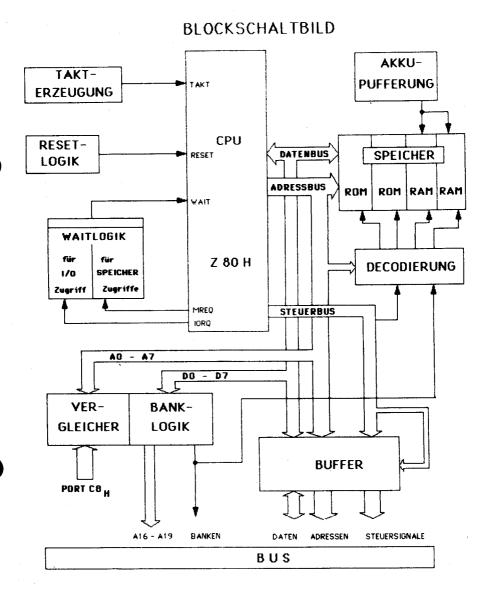

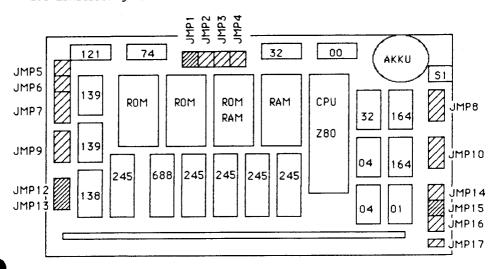

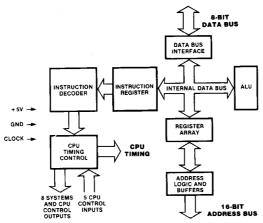

#### 3.1 Blockschaltbild SBC3

#### 3.2 Beschreibung des Blockschaltbildes und Schaltungsprinzip

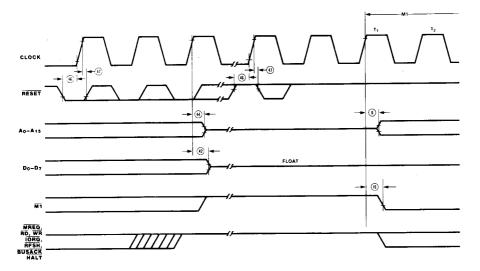

Die CPU Z80 ist das Herz der Schaltung. Sie steuert zentral alle Abläufe des Computers. Einsetzbar sind die Z80-Typen Z80, Z80A, Z80B und Z80H. Damit die CPU vernünftig arbeiten kann braucht sie eine Taktversorgung und eine RESET-Logik. Der Takt bestimmt die Arbeitsgeschwindigkeit der CPU. Die RESET-Logik muß dafür sorgen, daß bei Tastendruck oder beim Einschalten des Computers ein RESET durchgeführt wird. Dazu ist es notwendig, daß für 3 Taktzyklen ein LOW-Signal am RESET-Eingang der CPU anliegt. Erklärung RESET: RESET bedeutet Rücksetzen und setzt die CPU in den Anfangszustand zurück.

Die Speicher sind die Arbeitsebenen der CPU. Vom Speicher holt er sich die Befehle die er dann ausführt, legt dort Daten ab, holt sie wieder etc. Dabei gibt es grob umrissen zwei Typen von Speichernis ROMs und RAMs. ROM ist die Abkürzung für "READ ONLY MEMORY" und bedeutet, daß von diesem Speicher nur gelesen werden kann. Die Speicherinformationen (Programme) sind dort fest eingebrannt und bleibt auch nach Abschalten der Spannungsversorgung erhalten. Das EPROM ist ein weiterentwickeltes ROM, das mit UV-Licht gelöscht werden kann. RAM ist die Abkürzung für "RANDOM ACCESS MEMORY" und bedeutet, daß auf diesen Speicher geschrieben und von ihm gelesen werden kann. Der Nachteil an diesen Speichern ist, daß nach Abschalten der Versorungsspannung die Speicherinformation gelöscht wird. Deshalb wurde hier bei der SBC3 eine Akku-Pufferung vorgesehen, die nach Abschalten der Spannungsversorgung die RAMs mit Strom versorgt.

Die BANK-AUSWAHL-LOGIK wird nur benötigt, wenn die SBC3 im CP/M-System eingesetzt wird. Hier dient sie dazu den Adressraum des ZBO auf 1 Mbyte zu erhöhen. Zum "booten" des Betriebssystems werden die Speicher auf der SBC3 verwendet. Das Betriebssystem wird von der Diskette auf eine Speicherbank geladen, die dann aufgerufen wird.

Die BUFFER dienen dazu den Datenbus, Adressbus und Steuerbus zu verstärken und auf den BUS weiter zu geben.

Die WAIT-Logik muß nur dann eingesetzt werden, wenn sie mit der CPU ZBØH mit 8 MHz ihr System betreiben. Dabei können entweder die Speicher oder irgendwelche EIN/AUSGABE-Einheiten für die CPU zu langsam sein. Die WAIT-Zyklen können für Speicher und EIN/AUSGABE-Einheiten getrennt eingestellt werden (bis zu je 4 WAIT-Zyklen).

#### 3.3 Prinzipbeschreibung CP/M und "booten"

Das Betriebssystem CP/M benötigt einen RAM-Bereich von 0000H beginnend. Dies kann mit Hilfe der Bankumschaltung erreicht werden. Das Betriebssystem ist aber auf Diskette gespeichert und muß in den RAM-Bereich geladen werden. Um das Betriebssystem in diesen Bereich zu laden, verwendet man das Prinzip des "Bootstrap-Loaders". D.h. der Monitor (Flomon) lädt das Betriebssystem von der Floppy-Disc in den RAM-Bereich und springt nach dem Laden in den RAM-Bereich und startet das eben geladene Betriebssystem CP/M. Diesen Vorgang bezeichnet man als "booten".

Dabei sitzt auf der SBC3 das "Boot-EPROM" (FLOMON). Der RAM-Bereich in den das CP/M geladen wird, muß durch eine ROA64k oder eine RAM64/256 zur Verfügung gestellt werden. Aber es wird keine BANKBOOT mehr benötigt.

#### 4. Aufbauanleitung

#### 4.1 CMOS-Warnung

CMOS-Bausteine sind hochempfindlich gegen elektrostatische Aufladung! Bewahren oder transportieren Sie CMOS-Bausteine nur auf dem leitenden Schaumstoff! (Alle Pins müssen kurzgeschlossen sein).

Tip: Fassen Sie an ein geerdetes Teil (z.B. Heizung, Wasserleitung oder an den Schutzkontakt der Steckdose, bevor Sie einen Baustein berühren.

Bitte beachten Sie hierzu auch den Artikel "Schutzmaßnahmen für MOS-Schaltungen" in unserer Zeitschrift LOOP3.

Bei der SBC3 sind die RAM 8k oder RAM 2k CMOS-Bausteine.

#### 4.2 Stückliste

|                                                          | DOGORIIB                                                                      |                                                                                                                                                                                    |                                                                                       |                                                                                                                                                                                            |

|----------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                        | 10389                                                                         | Original GES-Plat<br>druck r4                                                                                                                                                      | tine mit Lötsto                                                                       | oplack und Bestückungs-                                                                                                                                                                    |

| 1                                                        | 10388                                                                         | Handbuch Ausgabe                                                                                                                                                                   | 2                                                                                     |                                                                                                                                                                                            |

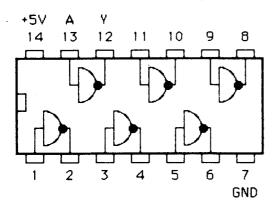

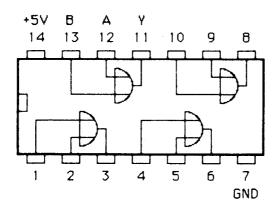

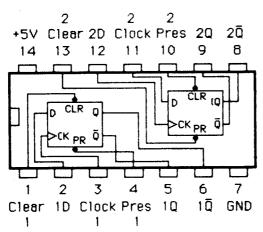

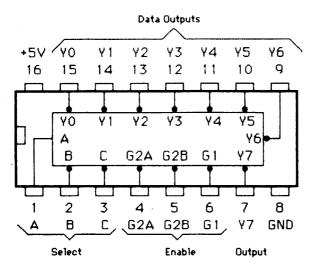

| 1<br>1<br>1<br>1<br>2<br>1<br>1<br>2<br>2<br>4<br>1<br>1 | 60095<br>60102<br>60115<br>60118<br>60135                                     | 74 04<br>74 121<br>74 LS 00<br>74 LS 01<br>74 LS 04<br>74 LS 32<br>74 LS 74<br>74 LS 138<br>74 LS 139<br>74 LS 164<br>74 LS 245<br>74 LS 245<br>74 LS 273<br>74 LS 688<br>CPU Z80A | J1<br>J4<br>J24<br>J14<br>J3,J11<br>J2<br>J16<br>J5,J13<br>J12,J14                    | 6 Iverter Monoflop 4 NAND 4 NAND (open Collector) 6 Inverter 4 OR 2 D-Flip-Flop 3 zu 8 Dekoder 2 zu 4 Dekoder 8-Bit Schieberegister 8-Bit-Tri-State Bustreiber 8-Bit Größenvergleicher CPU |

| ī                                                        | 10357                                                                         | RAM 8k                                                                                                                                                                             |                                                                                       | RAM-Speicher 8kbyte                                                                                                                                                                        |

| 1                                                        | 60179                                                                         |                                                                                                                                                                                    | Q 1                                                                                   | Quarz 8 MHz                                                                                                                                                                                |

| 11<br>2                                                  | 60239<br>60248                                                                | 100 nF<br>10 uF                                                                                                                                                                    | C1, C2, C4-C12<br>C3, C13                                                             | Keramik-Kond. 100 nF<br>Tantal-Kond. 10 uF                                                                                                                                                 |

| 9<br>1<br>2<br>3<br>1<br>1<br>1<br>1                     | 60626<br>60617<br>60627<br>60648<br>60746<br>60631<br>60643<br>60519<br>60518 | 1k<br>10k<br>2,2k<br>4,7k<br>68<br>220<br>330<br>8*1k<br>8*3.3k                                                                                                                    | R1, R2,<br>R12 - R18<br>R10<br>R7, R8,<br>R4, R5, R9<br>R3<br>R6<br>R11<br>RN2<br>RN1 | Widerstände 1 kOhm Widerstände 2,2 kOhm Widerstände 2,7 kOhm Widerstande 68 Ohm Widerstand 220 Ohm Widerstand 330 Ohm Netzwerkw. 8*1 kOhm Netzwerkw. 8*3,3 kOhm                            |

| 1                                                        | 60290                                                                         | 1N4148                                                                                                                                                                             | D1                                                                                    | Si-Diode                                                                                                                                                                                   |

| 4                                                        | 60486                                                                         | Mod 225H                                                                                                                                                                           |                                                                                       | Shunt-Stecker                                                                                                                                                                              |

| 1<br>2                                                   | 60502                                                                         |                                                                                                                                                                                    | JMP12, JMP13<br>JMP1, JMP15                                                           |                                                                                                                                                                                            |

| 2                                                        | 60603                                                                         | BSX 20                                                                                                                                                                             | TR1, TR2                                                                              | Transistoren                                                                                                                                                                               |

| 1                                                        | 60221                                                                         | NCM-2,4                                                                                                                                                                            | Akku                                                                                  | Akku 2,4 V                                                                                                                                                                                 |

| 1                                                        | 60301                                                                         |                                                                                                                                                                                    | S1                                                                                    | Taster für RESET                                                                                                                                                                           |

| 1 | 10406 | ST 1 |           | Steckerleiste |

|---|-------|------|-----------|---------------|

| 1 | 10405 | ST 1 | 18-polige | Steckerleiste |

| 1 | 60193 |      | 40-polige | IC-Fassung    |

| 4 | 60190 |      | 28-polige | IC-Fassung    |

| 6 | 60187 |      | 20-polige | IC-Fassung    |

| 3 | 60185 |      | 16-polige | IC-Fassung    |

| 9 | 60183 |      | 14-polige | IC-Fassung    |

|   |       |      |           |               |

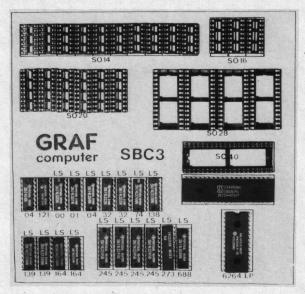

Abb.: ICs und Sockel der SBC3

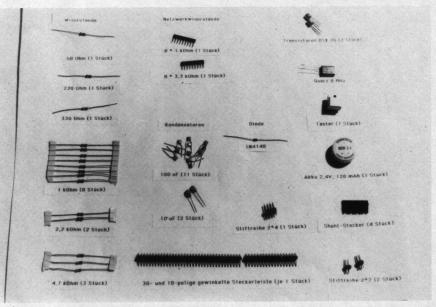

Abb.: Einzelne Bauteile der SBC3

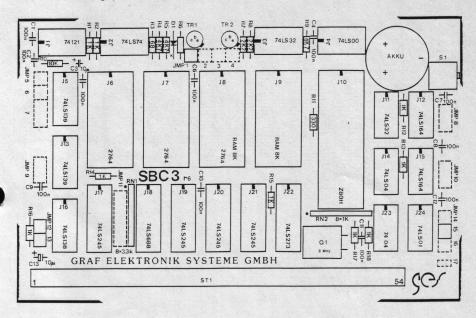

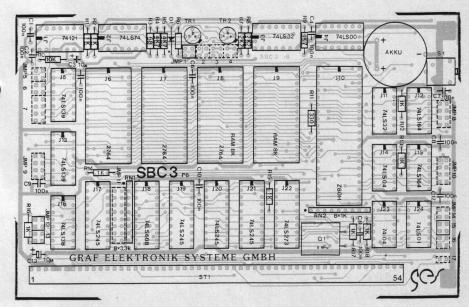

#### 4.3 Bestückungsplan

#### 4.4 Layout Bestückungsseite mit Bestückungsplan

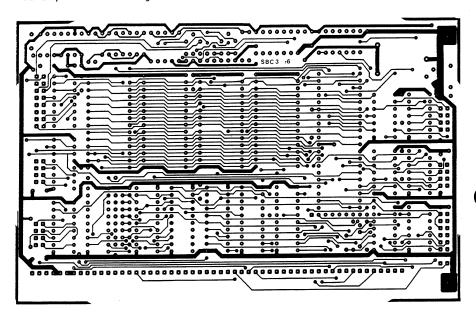

#### 4.5 Layout Bestückungsseite

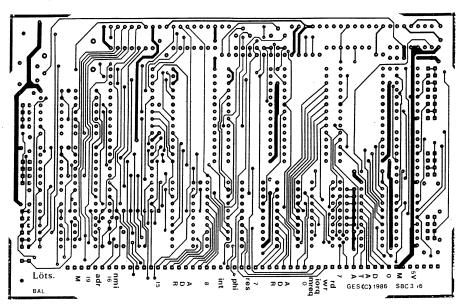

#### 4.6 Layout Lötseite

#### 4.7 Aufbau Bohritt für Sohritt

Auf einer Seite der Leiterplatte steht der Hinweis "löts" (Lötseite); auf dieser Seite wird ausschließlich gelötet. Die Bauteile sind nur auf der anderen Seite aufzustecken, der Bestückungsseite. Beim Einlöten der Bauelemente beginnt man am besten mit der gewinkelten Steckerleiste. Es sollte darauf geachtet werden, daß die Leiste parallel zur Leiterplatte liegt, um gut auf den Bus gesteckt werden zu können. Dabei sollten zuerst die beiden äußeren Stifte und einer in der Mitte verlötet werden. Dann empfiehlt es sich nachzuschauen, ob die Stecker parallel zur Platine liegen und ob keine "Bäuche" zwischen den verlöteten Stiften liegen. Sollten "Bäuche" vorhanden sein, muß wiederum in der Mitte der "Bäuche" ein Stift unter Druck angelötet werden. Liegt die Steckerleiste dann richtig, können die restlichen Stifte verlötet werden.

Nun wird die Leiterplatte mit den IC-Sockel bestückt. Dabei muß darauf geachtet werden, daß die Sockel richtig aufgesteckt werden. Im Bestückungsplan sind die Richtungen mit einer Kerbe gekennzeichnet. Sie muß mit der Richtung der Kerbe in der Fassung übereinstimmen. Außerdem ist die Lage der Fassungen auch auf der Bestückungsseite der Leiterplatte durch den Aufdruck sehr deutlich zu erkennen, oder auf dem Bestückungsplan, wenn kein Bestückungsdruck vorhanden.

Es sollten alle Fassungen auf einmal aufgesteckt werden und zum Verlöten umgedreht werden; dabei ist es hilfreich, wenn man beim Umdrehen die Fassungen mit einem Stück Karton auf die Leiterplatte drückt. So wird erreicht, daß die Fassungen alle eben und gerade liegen. Beim Löten sollten wiederum nur zwei Pins jeder Fassung (möglichst diagonal) verlötet werden. So können anschließend schräg liegende Fassungen noch problemlos korrigiert werden. Bevor die restlichen Pins verlötet werden, sollte noch auf die Bestückungsseite geschaut werden, ob die Fassungen richtig liegen und die Richtungen der Fassungen stimmen.

Die Kondensatoren C3 und C13 sind gepolt und dürfen auf keinen Fall falsch herum eingelötet werden. Der Pluspol ist mit einem "+" gekennzeichnet. Im Bestückungsplan ist der Pluspol ebenfalls mit einem "+" gekennzeichnet.

Die Kondensatoren C1, C2 und C4 bis C12 sind ungepolt und können ohne auf die Polung zu achten eingelötet werden.

Die Netzwerkwiderstände RN1 (8\*3,3 kOhm) und RN2 (8\*1 kOhm) haben einen gemeisamen Anschluß der mit einem Punkt am Bauelement und auf dem Bestückungsplan gekennzeichnet ist. Die Größe der Netzwerkwiderstände sind nicht durch Farboode ausgedrückt, sondern durch drei Ziffern. Dabei entsprechen die ersten beiden Ziffern den Anfangsziffern des Widerstandswertes und die dritte Ziffer die Zehnerpotenz, also die Anzahl der anzuhängenden Nullen. Beim 1 kOhm Netzwerkwiderstand steht der Zahlenwert "102" drauf, also 10 und zwei Nullen = 1 kOhm. Beim 3.3 kOhm Netzwerkwiderstand ist der Wert "332" aufgedruckt. Die anderen Aufdrucke mit Ausnahme des Punktes sind hier nicht von Bedeutung.

Die Widerstände R1 bis R18 sind Einzelwiderstände mit Farbcode. Die verwendeten Widersände im Farbcode:

#### Widerstandswerte

68 Ohm 220 Ohm

330 Ohm 1 kOhm

2,2 kOhm 4,7 kOhm

10 kOhm

#### Farbcode

blau - grau - schwarz rot - rot - braun orange - orange - braun

braun - schwarz - rot

rot - rot - rot

gelb - violett - rot braum - schwarz - orange Wie aus der Tabelle hervorgeht sind für die Widerstandswerte die ersten drei Ringe ausschlaggend. Der vierte Ring dient nur zur Toleranzangabe und ist meistens "gold".

Die Diode D1 ist gepolt und darf nicht falsch herum eingelötet werden. Die Kathode ist auf der Diode mit einem Strich gekennzeichnet. Auf dem Bestückungsplan ist die Kathode mit einem "K" beschriftet.

Die beiden Transitoren TR1 und TR2 haben drei Anschlüße: Basis, Emitter und Collector. Auf dem Bestückungsplan sind die Anschlüße mit B, C und E bezeichnet. Am Transistor ist der Anschlüßpin der der "Nase" am Transistorgehäuse am nächsten kommt der Emitter. Der mittlere PIN ist die Basis und der dem Emitter gegenüberliegende der Collector. Der Transistor kann einfach eingesetzt werden, ohne daß die Beinchen gekreuzt werden müssen.

Der Quarz Q1 ist ungepolt und sollte möglichst liegend eingelötet werden. Dabei sollten Sie aber darauf achten, daß das Gehäuse des Quarzes nicht die Leiterplatte berührt, und damit Kurzschlüsse zwischen Leiterbahnen verursachen könnte. Sie könnten aber auch etwas Isoliermaterial (z.B. etwas Papier) unter den Quarz legen um dies sicher zu verhindern.

Die beiden Stiftreihen 2\*2 werden an JMP1 und an JMP15 eingesetzt. Die Stiftreihe 4\*2 wird an JMP12 und JMP13 eingesetzt. Die Shuntstecker werden je nach Systemkonfiguration gesteckt (siehe Einstellung der JMP).

Der Taster S1 kann aufgrund der Bohrungen auf der Leiterplatte nicht falsch herum eingelötet werden.

Falls die SBC3 ins GEH3 (Art. Nr. 10673) eingebaut werden soll, benötigen Sie das Rückwandblech für CPU's (Art. Nr. 10828). Dieses Rückwandblech wird zum einen an die Leiterplatte mit zwei Schrauben festgeschraubt, und zum anderen an die Rückwand des Gehäuses. Damit ist die Baugruppe fest justiert.

Der Akku "NCM 2,4" hat drei Beinchen wobei 2 für den "+" Pol sind und einer der "-" Pol. Infolge der Rasterung auf der Platine kann der Akku nicht falsch herum eingelötet werden. Falls die Bohrungen für den Akku zu klein sind, müssen Sie die Beinchen des Akku mit einer Flachzange etwas quetschen, oder Sie löten den Akku einfach nur auf die Bohrungen auf.

#### 5. Testanleitung

#### 5.1 Erste Prüfung ohne ICs

Die Platine ist bis jetzt erst mit den Sockeln und mit den passiven Bauelementen bestückt. Mit diesem Aufbau werden die ersten Tests durchgeführt.

Wenn Sie den Akku und die Diode richtig bestückt haben müssen an Pin 28 der IC-Sockel IC8 und IC9 jeweils ca. 2,5 V anliegen. Dies ist die Pufferspannung für die RAMs.

Zum nächsten Test muß die Baugruppe in den Bus gesteckt werden. Achten Sie beim Einstecken in den Bus, daß Sie die Baugruppe richtig herum einsetzen. Ein falsches Einstecken, z.B. um ein Pin zu weit rechts kann zu Kurzschlüssen führen und kann Bauelemente zerstören.

Man mißt, ob an allen IC-Sockeln die Versorgungsspannung von +5V ankommt. Dabei liegt jeweils am letzen Pin eines (z.B. bei 14-poligen an Pin 14) liegt die Versorgungsspannung von +5V. OV bzw Masse liegt jeweils auf dem letzten Pin der ersten Reihe (bei 14-poligen auf Pin 7, bei 16-poligen auf Pin 8, bei 20-poligen auf Pin 10).

An Pin 28 der ICs 8 und 9 liegen jetzt ca. 4,5 V. Das kommt davon, daß an der Diode ca. 0.7V abfallen. Liegt die Spannung unter 4,5 V ist die Spezifikation für die Speicher nicht mehr erfüllt. Trotzdem läuft die Schaltung fast in jedem Falle, da diese CMOS-RAM relativ unempfindlich gegen Versorgungsspannungserniedrigung sind.

Liegt die Versorgungsspannung +5V und OV (Masse) an den richtigen Pins an können die ICs eingesetzt werden. Dabei muß auf die Richtung der ICs geachtet werden. Die Markierung auf dem IC muß mit der Kerbe in der Fassung übereinstimmen.

#### 5.2 Test im System

#### 5.2.1 Test im HEX-System

Konfigurieren Sie Ihr System, wie in Punkt 1.3 dargestellt. Das EPROM EHEX2 wird auf den Einbauplatz IC6 gesteckt. Und mindestes ein RAM 8k muß gesteckt werden (IC8). Die JMP müssen jeweils in Stellung 1 gestellt sein (siehe 5.3.1). Sie können auch die Speicher die auf der SBC2 verwendet werden, allerdings müssen Sie dann die entsprechende Speicherkonfiguration an den JMP einstellen (siehe 5.4). Funktioniert die Baugruppe, so muß nach dem Einschalten das "Hallo-1.1" erscheinen.

#### 5.2.2 Test im System mit Tastatur und Bildschirm ohne CP/M

Konfigurieren Sie Ihr System wie unter 1.3 erläutert. Stecken Sie das EPROM EGRUND2 auf den ersten Einbauplatz (IC6), der zweite (IC7) kann leer bleiben. Es kann aber auf diesen auch EGOSI2 oder ESPS2 gesteckt werden. Außerdem wird mindestes ein RAM 8k benötigt (IC8). Die JMP müssen wie unter 5.3.1 gesteckt werden. Verwenden Sie andere Speicher müssen Sie die JMP entsprechend der Speicherkonfiguration (siehe unter 5.4) eingestellt werden. Wenn Sie das System jetzt einschalten, muß das Grundmenu auf dem Bildschirm erscheinen.

#### 5.2.3 Test im System mit CP/M

Konfigurieren Sie Ihr System wie unter Punkt 1.3. Auf dem ersten Steckplatz (J6) wird das EPROM "FLOMON" gesteckt. Auf dem vierten Steckplatz (J9) muß ein 8k RAM stecken. Haben Sie noch das alte FLOMON V1.5 müssen zwei 8k RAMs (J8 und J9) gesteckt sein. Die JMP müssen dann wie unter 5.3.2 beschrieben gesteckt sein. Es kann auch

die gleiche Speicherkonfiguration wie auf der BANKBOOT gewählt werden, dann muß aber die entsprechende Speicherkonfiguration mit den JMP eingestellt werden (siehe unter 5.4). Wenn Sie jetzt einschalten muß auf dem Bildschirm das kleine Menu mit "1 = Floppy Boot" "2 = Bank E0000H" usw, erscheinen.

#### 5.2.4 Test mit dem ZEAT-System

Konfigurieren Sie das System wie beim CP/M-System. Das 8k EPROM "FLOMON" wird auf den ersten Steckplatz gesteckt. Die beiden EPROMS "ZEAT A" und "ZEAT B" werden auf die Einbauplätze 2 und 3 (J7, J8) gesteckt. Ein 8k RAM muß auf Steckplatz 4 (J9) gesteckt werden. Wenn Sie jetzt einschalten, muß dasselbe Menu wie beim CP/M System erscheinen. Wählen Sie Punkt 4 des Menu an, muß das Christiani ZEAT Menu erscheinen.

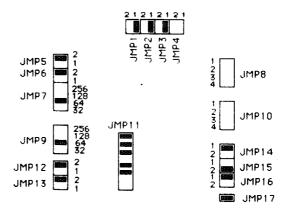

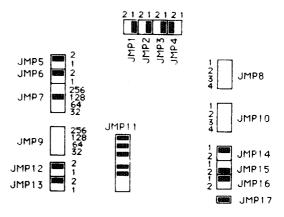

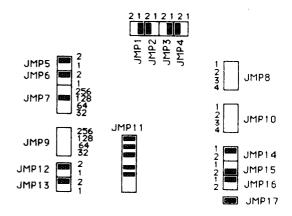

#### 5.3 Einstellung der JMP

Skizze: Bestückungsplan mit JMP

Die stark schraffierten JMP (JMP1, JMP12, JMP13 und JMP15) sind "offene" JMP und müssen von Ihnen eingestellt werden. Die restlichen JMP (leicht schraffiert) sind auf der Lötseite voreingestellt und müssen normalerweise nicht geändert werden. Diese JMP müssem sie ändern, wenn Sie keine 8k Speicher verwenden, wenn Sie die CPU Z8DH mit 8 MHz einsetzen wollen oder wenn Sie den Takt zum Bus trennen wollen usw.

#### Einstellung der offenen JMP mit "Shunt-Stecker"

Dabei handelt es sich um die JMP1, JMP12, JMP13 und JMP15. Mit diesen 4 JMP kann die SBC3 als "Single Board Computer", ohne CP/M (bisher SBC2 oder CPU ZBØ mit ROA64k) oder als zentrale Baugruppe für CP/M (bisher CPU ZBØ und BANKBOOT) mit FLOMON oder mit ZEAT (Assembler von Christiani) verwendet werden. Vorausgesetzt ist dabei, daß 8k-EPROMS (2764) und 8k-RAMs eingesetzt werden.

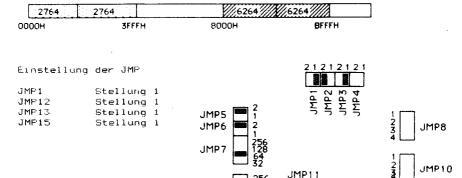

#### 5.3.1 System mit Tastatur und Bildschirm ohne CF/M

Bei diesem System können maximal 2 EPROMs 2764 und 2 RAM 8k eingesetzt werden (32k).

Speicherkonfiguration:

JMP9

JMP12

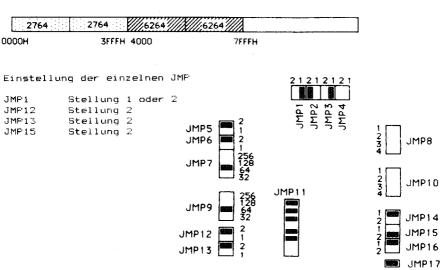

#### 5.3.2 System mit CP/M

Bei diesem System können auch maximal 2 EPROMs 8k und 2 RAMs 8k eingesetzt werden. Auf der Adresse 2000H kann noch das Grundprogramm EGRU2000, oder EGDSI2 usw. stecken.

JMP16

Speicherkonfiguration:

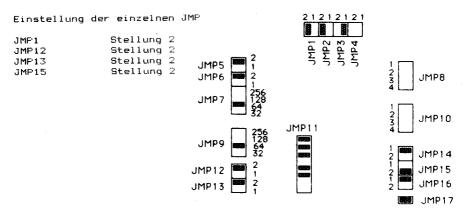

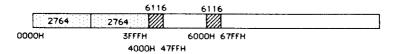

#### 5.3.3 System mit CP/M und ZEAT

Bei diesem System werden 3 EPROMS 8k und 1 RAM 8k eingesetzt.

Speicherkonfiguration:

| 2764 2764 | 2764 ///6264 |       |

|-----------|--------------|-------|

| 0000Н     | SFFFH 6000H  | 7FFFH |

Dies sind die drei Einstellungen, mit denen die SBC3 normalerweise betrieben wird. Wollen Sie andere Speicher als 8k Speicher verwenden oder die CPU ZBØH mit 8 MHz dann müssen Sie die voreingestellten JMP "anrühren".

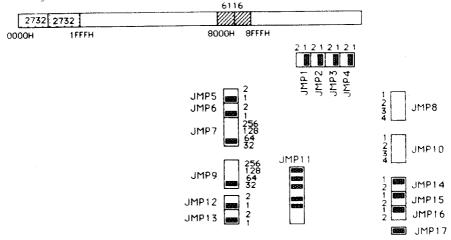

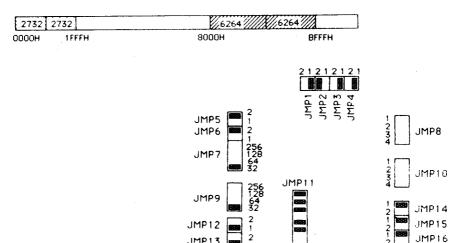

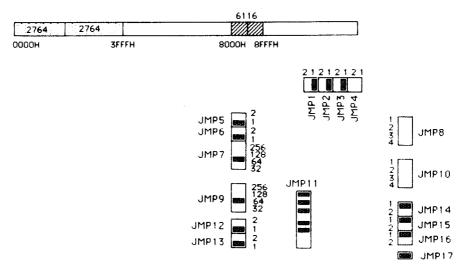

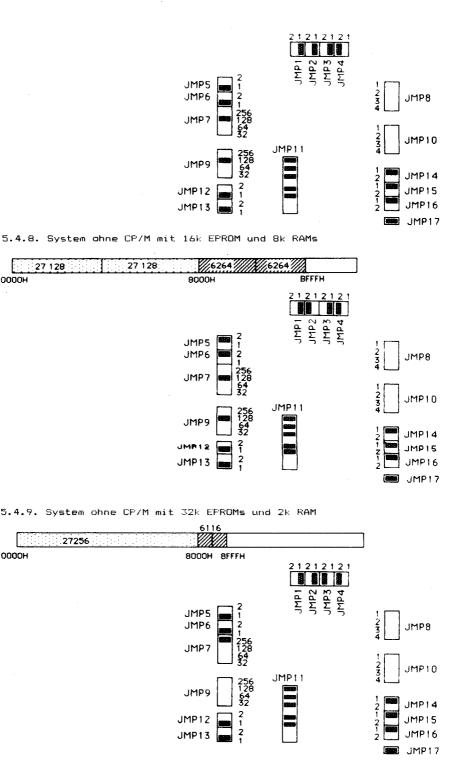

#### 5.4 Speicherkonfigurationen und dazugehörige Jumperstellungen

- 5.4.1. System ohne CP/M mit 8k EPROMs und 8k RAMs (siehe 5.3.1)

- 5.4.2. System mit CP/M mit 8k EPROMs und 8k RAMs (siehe 5.3.2)

- 5.4.3. System mit CP/M und ZEAT mit 8k EPROMs und 8k RAM (siehe 5.3.3)

5.4.4 System ohne CP/M mit 4k EPROMS (2732) und 2k RAMs (6116): Konfiguration wie SBC2

#### 5.4.5. System ohne CP/M mit 4k EPROMs und 8k RAMs

JMP17

5.4.6. System ohne CP/M mit 8k EPROMs und 2k RAMs

5.4.7 System ohne CP/M mit 16k EPROMs und 2k RAMs

|           | 6116        |  |

|-----------|-------------|--|

| 27 128 27 | 7 128       |  |

| 0000H     | 8000H 8FFFH |  |

27 128

27256

0000H

0000H

#### 5.4.10. System ohne CP/M mit 32k EPROMs und 8k RAMs

5.4.11. System mit CP/M mit 8k EPROMs und 2k RAMs (wie BANKBOOT)

JMP13

JMP17

5.4.12. System mit CP/M mit 16k EPROMs und 2k RAMs

|       | 6116      | 6116        |  |

|-------|-----------|-------------|--|

| 2712  | 8         |             |  |

| 0000H | 3FFFH     | 6000H 67FFH |  |

|       | 4000H 47F | FH          |  |

5.4.13 System mit CP/M mit 16k EPROMs und 8k RAMs

Verwenden Sie das System ohne CP/M und ohne Floppy-Laufwerke können Sie im Höchstfall 1 EPROM 27256 verwenden, da nur 32k ROM-Bereich sinnvoll sind. Beim CP/M-System sind nur 16k ROM vorgesehen, deshalb kann im Höchstfall nur 1 EPROM 27128 und kein EPROM 27256 verwendet werden. Ausnahme: Beim ZEAT-System von der Firma Christiani werden 3 EPROMs 2764 (8K) verwendet, also ein ROM/Bereich von 24k und ein RAM Bereich von 8k mit einem RAM 6264 (8k). Dies funktioniert aber nur beim ZEAT-System; bei diesem System wurde auch das FLOMON entsprechend geändert. Für dieses ZEAT-System muß der JMP1 in Stellung 2 stehen (Spannungsversorgung vom Akku trennen).

#### 5.5 Allgemeine Erklärung der JMP

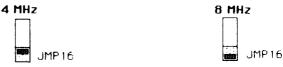

JMP16:

Dieser JMP dient dazu den Takt von 4 MHz auf  $\theta$  MHz umzustellen (siehe Abb.)

JMP10 und JMP11:

Mit diesen beiden JMP können Sie ein bis vier WAIT-Zyklen, getrennt für I/O-Zugriff und Speicherzugriff einstellbar. Die WAIT-Zyklen werden nur benötigt, wenn Sie mit der CPU Z80H arbeiten (siehe Punkt 5.6).

JMF14:

JMP14 dient dazu, daß die WAIT-Logik für Speicher grundsätzlich bei jedem Speicherzugriff oder nur bei Speicherzugriff der auf der Baugruppe befindlichen Speicher, gestartet wird. In Stellung 1 wird die WAIT-Logik bei jedem Speicherzugriff gestartet; in Stellung 2 nur bei Zugriff auf Baugruppeninterne Speicher. Verwenden Sie die CPU Z8ØA brauchen Sie normalerweise keine WAIT-Zyklen und deshalb ist dann dieser JMP für Sie nicht von Bedeutung.

# WAIT bei jedem Speicherzugriff JMP14 WAIT nur bei internem Speicherzugriff JMP14

JMP17:

Dieser JMP ist lediglich dazu da den Takt der CPU auf den BUS zu legen oder ihn vom BUS zu trennen. Interessant ist der JMP wenn Sie die Taktleitung des BUSSES mit dem Takt einer anderen Baugruppe belegen wollen. In diesem Fall müssen Sie JMP17 auftrenen.

JMP2, JMP3 und JMP4:

Diese drei Jumper sind für dazu da die verschiedenen Einsetzbaren Speichertypen "Pinkompatibel" zu machen. Verwenden Sie nur 8k EPROMs und 8k RAMs sind diese JMP voreingestellt und müssen nicht geändert werden. Verwenden Sie aber andere Speicher müssen diese JMP eingestellt werden. Siehe hierzu "Speicherkonfiguration und dazugehörige Jumperstellungen".

#### JMP6 und JMP7:

Diese beiden JMP dienen dazu den CS für die verschiedenen einsetzbaren EPROM-Typen einzustellen. Hier sind die Stellungen 32, 64, 128 und 256 für die EPROMs 2732, 2764, 27128 und 27256. Für das erste EPROM (J6) gilt JMP7, für das zweite EPROM (J7) gilt JMP9. Hier muß allerdings gesagt werden, daß immer nur zwei gleiche EPROM-Typen verwendet werden dürfen. Diese JMP sind für 8k EPROMs (2764) in Stellung "64" voreingestellt. Genaue Einstellung siehe unter "Speicherkonfigurationen und dazugehörige Jumperstellung".

JMP5. JMP6, JMP12, JMP13 und JMP15:

Diese 5 Jumper dienen dazu den CS für die verschiedenen einsetzbaren RAM-Typen einzustellen. Da sich der RAM Bereich beim System mit CP/M und beim System ohne CP/M ändert sind hierzu fünf Jumper nötig. JMP5 und JMP6 sind für 8k RAM-Bausteine (z.B. 6264) fest eingestellt. Die anderen drei Jumper sind variabel (siehe oben unter "Systemkonfiguration und dazugehörige Jumperstellung").

#### 5.6 Betrieb mit der CPU Z8ØH mit 8 MHz

Wollen Sie die CPU Z80H einsetzen, müssen Sie folgende JMP ändern.

Der Takt-Jumper (JMP16) muß auf der Lötseite aufgekratzt werden, und dann mit Lötbrücke in Stellung 2 einstellen (siehe Abb.).

2. Sie müssen, wenn Sie langsame Speicher oder langsame I/O Einheiten haben, WAIT-Zyklen einfügen. Dies geschieht mit den JMP8 und JMP10 und zwar getrennt für I/O-Zugriffe und für Speicherzugriffe. Sollte also die GDP64k oder die FLO2 Schwierigkeiten machen empfiehlt es sich zwei oder drei WAIT-Zyklen für I/O-Zugriffe einzufügen. Ein WAIT-Zyklus bei I/O-Zugriffen ist nicht sinnvoll einzustellen, da die CPU bei jedem I/O-Zugriff automatisch einen WAIT-Zyklus einfügt. Einstellung WAIT für I/O-Zugriff an JMP8: siehe Abb..

|                                                                                      | JMP8  |

|--------------------------------------------------------------------------------------|-------|

| Beispiel 1:<br>kein WAIT-Zyklus für Speicherzugriff<br>2 WAIT-Zyklen für I/O-Zugriff | JMP10 |

|                                                                                      | JMP8  |

| Beispiel 2:<br>2 WAIT-Zyklen für Speicherzugriff<br>2 WAIT-Zyklen für I/O-Zugriff    | JMP10 |

Sind Ihre Speicher zu langsam (kann nur bei 8 MHz (Z8ØH) vorkommen) müssen sie an JMP1 ein oder zwei WAIT-Zyklen einstellen. Meistens genügt ein WAIT-Zyklus. Mehr als zwei WAIT-Zyklen werden so gut wie nie benötigt. Einstellung WAIT für Speicherzugriffe an JMP1Ø siehe Abb..

#### 6. Fehlersuchanleitung

#### 6.1Mögliche Fehler und ihre Behebung

- 6.1.1 Sind die bisher verwendeten Baugruppen in Ordnung? (Funktioniert das System ohne die Baugruppe

- 6.1.2 Sind die Jumper richtig gesteckt?

- 6.1.3 Machen Sie zuerst eine Sichtprobe. Können Sie irgendwo auf der Platine unsaubere Lötstellen (zuviel Lötzinn, manchmal zieht das Lötzinn Fäden) erkennen, die eventuell einen Kurzschluß verursachen könnten? Dann müssen sie diese Lötstellen nachlöten und die unzulässige Verbindung beseitigen.

- 6.1.4 Haben Sie auch alle ICs richtig herum und am richtigen Platz eingesteckt? (Vergleiche mit Bestückungsplan)

- 6.1.5 Sind alle gepolten Bauteile (Elkos, Dioden, usw.) richtig herum eingelötet?

- 6.1.6 Haben sie auch keine Lötstelle vergessen zu löten? (sehen sie lieber noch einmal nach)

- 6.1.7 Sehen Sie irgendwo "kalte" Lötstellen?

Kalte Lötstellen erkennt man daran, daß sie nicht

glänzen, sie sind im Vergleich mit richtg gelöteten

Lötstellen trübe.

- 6.1.8 Haben Sie auch nicht zu heiß gelötet? Wenn der Lötkolben zu heiß eingestellt ist und (oder) Sie zu lange auf der Lötstelle bleiben, dann kann es passieren, daß sich die Leiterbahnen von der Flatine lösen, und Unterbrechungen bilden. Ferner kann es auch passieren, daß Durchkontaktierungen unterbrochen werden, oder daß Bauteile durch zu heißes Löten zerstört werden.

- 6.1.9 Nehmen Sie alle ICs aus ihren Fassungen. Nehmen Sie sich die Layouts zur Hand und kontrollieren Sie alle Leiterbahnen, mit einem Durchgangsprüfer oder mit einem Ohmmeter, auf Durchgang. Bereits kontrollierte Leiterbahnen können Sie, der Übersicht wegen, auf Layout mit Bleistift durchstreichen oder mit Farbstiften nachziehen.

- 6.1.10 Prüfen sie die Versorgungsspannung mit einem Digitalvoltmeter (am Bus +5 Volt, nicht am Netzgerät, da am Kabel bei

starker Belastung bis zu 0.5 Volt abfallen können).

Toleranzen von +- 5% also von 4,75V bis 5,25V sind erlaubt.

Falls die Spannung zu gering ist, prüfen Sie, ob die Verbindung vom Netzteil zum Bus mit ausreichend dicker Litze

(mind. 2 mm @uadrat) erfolgt ist. Gegebenenfalls müssen

Sie Ihr Netzteil nachregeln. Vorsicht: Nie über 5.25V

nachregeln!

Wenn Sie alle Leiterbahnen kontrolliert haben und nichts gefunden haben, dann ist die Wahrscheinlichkeit groß, daß ein Bauteil defekt ist.

Wenn Sie einen Prüfstift, oder ein Oszilloskop haben, dann können Sie jetzt überprüfen ob Sie an den jeweiligen Ausgängen die richtigen Signale haben. Welche Signale wo anliegen müssen können Sie aus der Schaltungsbeschreibung, aus dem Schaltplan und Ihren eigenen überlegungen folgern.

Falls Sie keine Meßgeräte haben, dann müssen Sie alle Bauteile systematisch austauschen, bis Sie das Defekte gefunden haben. Verwenden Sie dazu eventuell eine zweite Baugruppe (die eines Freundes oder eines Bekannten).

Sollten Sie gar nicht zurande kommen, hilft Ihnen unser Pauschal-Reparatur-Service, dessen Bedingungen Sie der Preisliste entnehmen können.

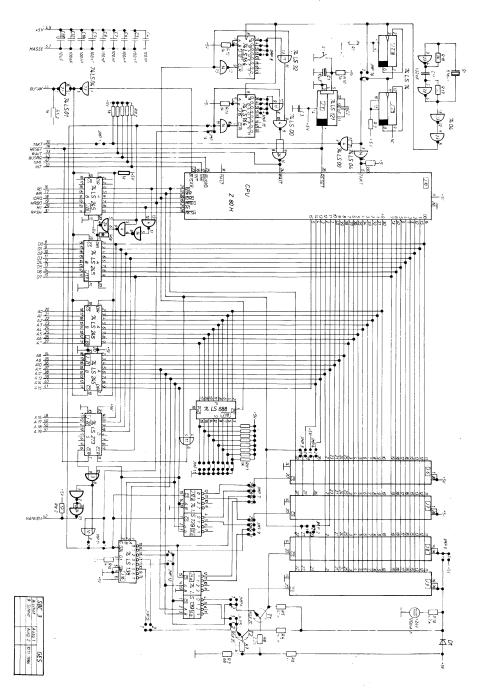

#### 7. Schaltungsbeschreibung

#### 7.1 Schaltplan

#### 7.2 Beschreibung der Schaltung SBC3

Wie aus dem Blockschaltbild ersichtlich kann die Schaltung in Blöcke aufgespalten werden. In der folgenden Schaltungsbeschreibung wird jeder Block getrennt beschrieben.

#### 7.2.1 Erzeugung des Taktes

Der Takt wird mit einem einfachen Prinzip erzeugt. Ein Inverter wird von seinem Ausgang auf den Eingang über einen 1k Widerstand zurückgeführt. Von diesen "Schwingern" sind zwei auf der Baugruppe, die mit einem 100 nF Kondensator (C11) miteinander verkoppelt sind. Der Quarz Q1 stabilisiert die Schwingung auf 8 MHz. Die Inverter (J23) geben dem Takt eine schöne Rechteckform. Die beiden D-Flip-Flop (J2) teilen die Taktfrequenz jeweils durch zwei. Am Ausgang des ersten Flip-Flops (J2/5) liegen 4 MHz und am Ausgang des zweiten (J2/9) 2 MHz (hier nicht beschaltet). Über JMP16 kann der Takt (4 oder 8 MHz) eingestellt werden. JMP16 ist hier voreingestellt auf 4 MHz

#### 7.2.2 RESET-Logik

Zum Rücksetzen der CPU in den Anfangszustand benötigt die CPU am RESET-Eingang einen negativen Impuls mit einer Mindestzeit von 3 Taktzyklen. Dieser negative Impuls wird mit dem Monoflop 74 121 (J1) erzeugt. Das Monoflop wird getriggert mit einem Taster. Um dabei ein prellfreies Triggersignal zu erhalten, wird die Triggerspannung über dem ELKO C3 abgegriffen. Dadurch steigt die Spannung am Elko C3 beim Loslassen des Tasters und beim Einschalten der Spannung langsam an und wird triggert bei einem best. Spannungswert das Monoflop. Bei diesem Triggereingang handelt es sich um einen Schmitt-Trigger Eingang, der die ansteigende Spannung sicher ab einem best. Spannungswert als HIGH erkennt. Ist das Monoflop getriggert, geht der Ausgang Q\* auf LOW. Die Länge dieses Signals wird durch den Kondensator C1 festgelegt.

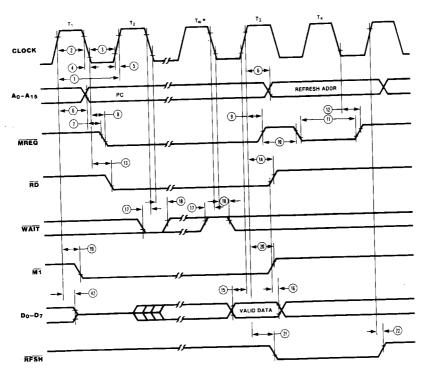

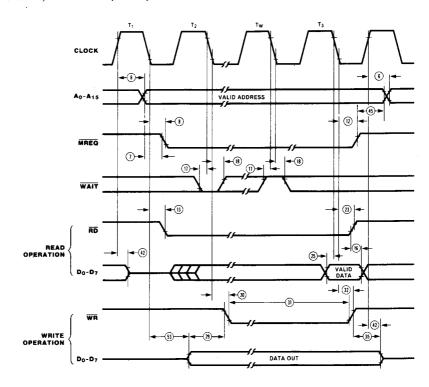

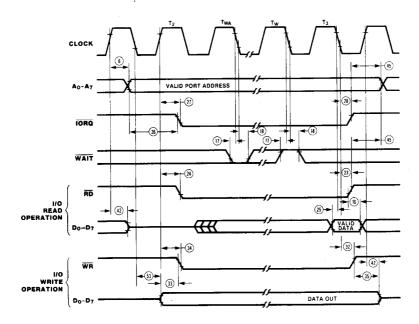

#### 7.2.3 WAIT-Logik

Die WAIT-Logik wird nur benötigt wenn die 8 MHz CPU verwendet wird. Die WAIT-Zyklen können getrennt für I/O und Speicherzugriff eingestellt werden. Bei den WAIT-Zyklen für Speicherzugriff kann noch einmal eingeschränkt werden: Mit JMP 14 kans die WAIT-Logik für Speicherzugriff bei jedem Zugriff auf Speicher, oder aber nur bei Zugriff auf die Speicher auf der Baugruppe, gestartet werden. Dieser JMP14 ist so voreingestellt, daß bei jedem Speicherzugriff die WAIT-Logik gestartet wird.

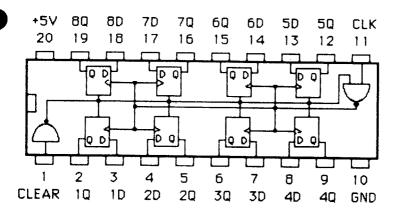

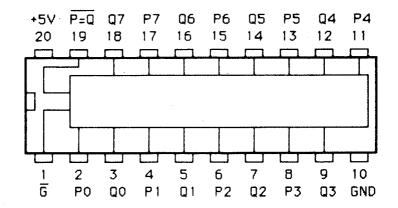

Wird auf keinen Speicher zugegriffen, dann ist das MREQ\*-Signal HIGH und das Schieberegister J15 wird gelöscht. Dadurch sind alle Ausgänge auf LOW. Wird dann auf einen Speicher zugegriffen, wird das Schieberegister nicht mehr gelöscht und schiebt ein HIGH Signale vom Eingang A und B mit jedem Taktsignal auf die parallelen Ausgänge QA bis QH. Bei jedem Taktimpuls wird ein Ausgang aktiviert, zuerst QA dann QB usw. Will man nun 2 WAIT-Zyklen einfügen, wird der Ausgang QB mit dem gemeinsamen Anschluß gebrückt. Dadurch erfährt das Signal eine Verzögerung von 2 Taktzyklen. Da dieses WAIT-Signal nur bei Speicherzugriff anliegen darf wird dieses Signal noch mit ODER verknüpft (J11). Die WAIT-Logik für I/O Zugriffe funktioniert im Prinzip genauso, nur wird hier zum Starten der WAIT-Logik das IORQ\*-Signal des Prozessors verwendet. Die beiden WAIT-Signale werden mit AND verknupft, (dies wird durch 2 NAND realisiert) d.h. sobald eines der beiden WAIT-Signale aktiviert (LOW) ist, wird der Ausgang des zweiten NAND (J24/10) und damit der Eingang WAIT LOW. Da noch das WAIT-Signal vom Bus auf diesen Eingang der CPU geht muß ein "Open Collector" NAND verwendet werden. Ein "Open Collektor" Gatter muß an seinem Ausgang aber mit einem 1k Widerstand auf +5V abgeschlossen werden. Einstellung der WAIT-Zyklen siehe unter 5.6.

#### 7.2.4 BANK-Auswahl-Logik

zur Verfügung stehen müssen, wird eine Logik benötigt, die mehr als 64 kbyte adressieren kann. Zu diesem Zweck werden mit Hilfe des Datenbusses die Adressen A16 bis A19 erzeugt, und auf einem LATCH gespeichert. Außerdem wird noch das Steuersignal diesselbe Weise erzeugt und ebenfalls auf den Bus gelegt. Zur Definition der Signale "Bank" und "Banken": Das Signal "Bank" liegt am Latch (J22/16) an, und das Signal "Banken" führt auf den Bus (ST1/42). Die einzelnen Speicherkarten (z.B ROA64k oder RAM64/256) dekodieren die Adressen A16 bis A19 wenn das Signal "Banken" auf HIGH liegt und je nach dem welche Kombination (A16 bis A19) anliegt, wird eine von 16 64 kbyte Banken angewählt. Ist das Signal "Banken" LOW, so werden die Speicher auf der SBC3 ausgewählt. Der Bank-Port auf dem die Adressen A16 bis A19 und das Signal "Bank" abgespeichert werden, wird über den Port C8H aktiviert. Die Adresse C8H ist an JMP11 voreingestellt. Der Baustein 74 LS 688 vergleicht die an JMP11 eingestellte Adresse mit der an den Adressen AO bis A7 anliegenden Adressen und aktiviert, wenn der Eingang G (mit IORQ\* beschaltet) LOW ist, den Ausgang P=Q\* (J18/19). Dieses Signal wird noch mit WR\* ODER verknüpft. Dadurch wird der Ausgang des ODER (J11/6) nur LOW, wenn auf den Port C8H geschrieben wird. Mit diesem Signal (J11/6) wird der CLK-Eingang des LATCHES 74 LS 273 gesteuert; d.h. wenn auf Port C8H geschrieben wird nimmt das LATCH Daten und gibt Sie an den Bus weiter. Die Daten (A16 bis A19 und Signal "Bank") bleiben auf den Ausgängen gespeichert und können mit einem LOW-Signal am Eingang "CLEAR" (J21/1) gelöscht werden. Dieser Eingang ist mit RESET verbunden, d.h. bei RESET werden die Adressen A16 bis A19 und das Bank-Signal auf LOW gesetzt. Das Signal "Bank" (J21/12) wird noch negiert und mit der negierten Adresse A15 NAND verknüpft, was einer OR Verknüpfung von Al5 und "Bank" gleichkommt. Das NAND wurde deshalb gewählt, weil das Signal "Banken" auf dem Bus auch von anderen Baugruppen gesteuert wird (COL256) und deshalb hier "Open Collektor" Gatter eingesetzt werden muß. Diese Bank-Auswahl-Logik wird nur bei CP/M benötigt und bei Betrieb ohne CP/M wird diese Logik mit dem JMP15 außer Kraft gesetzt.

Da der Z80 nur 64 kbyte adressieren kann und bei CP/M 2.2 64k

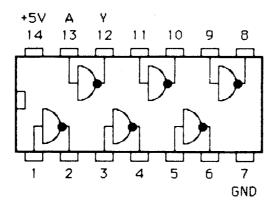

#### 7.2.5 Pufferung des Daten-, Adress- und Steuerbusses

Da die CPU auf der SBC3 sitzt und Daten, Adress- und Steuersignale erzeugt, die auf den Bus führen und von mehreren Baugruppen gelesen werden sollen, müssen diese Signale durch Treiber verstärkt werden. Diese Aufgabe übernehmen für den Daten-, Adress- und Steuerbus die bidirektionalen Tri-State Treiber 74 LS 245 (J17, J19, J20 und J21). Die Treiber für den Datenbus (J17) müssen die Daten in beide Richtungen weitergeben können. Daher wird der Eingang DIR (J17/1) mit dem RD\*, dem M1\*-Signal und dem Aktivierungssignal für die internen Speicher (J16/4) gesteuert. Diese Verknüpfung der drei Signale hat zur Folge, daß bei internem Speicherzugriff und bei externem Speicherschreibzugriff die Daten auf den Bus gelegt werden. Nur bei Lesezugriffen auf externe Speicherbanken werden die Daten vom Bus eingelesen. Die Verknüpfung mit dem M1-Signal bewirkt einerseits ein schnelleres einlesen vom Bus bei einem M1-Zyklus und andererseits ist dadurch das Einlesen eines Interrupt-Vektors

Mit dem Eingang CS können die A Ein- bzw Ausgänge von den B Ein- bzw Ausgängen getrennt werden (siehe Datenblatt 74 LS 245). Der Datenbus soll vom Bus getrennt werden, wenn das Signal BUSAK LOW ist.

Die Steuersignale und die Adressen müssen nur in einer Richtung verkehren; deshalb kann der Eingang DIR bei diesen LATCHES (J19, J20 und J21) auf festes Potential (+5V) gelegt werden. Der Eingang CS wird mit dem negierten BUSAK Signal gesteuert, d.h. wenn das BUSAK Signal LOW (aktiv) ist, werden sämtliche Steuersignale, die Adressen AO bis A15 und der Datenbus getrennt. Das Steuersignal BUSAK\* ist LOW wenn eine andere Einheit (sonst. CPU etc.) auf den Bus zugreifen will.

#### 7.2.6 Adressdekodierung

Die Adressdekodierung der Baugruppe ist sehr umfangreich, da 6 verschiedene Speichertypen einsetzbar sein sollen. Verwenden Sie die Speicherkonfiguration die von uns vorgeschlagen ist (8k EPROMs und 8k RAM) wird zur Speicherdekodierung nur noch der Dekoder 74 LS 138 Aufgabe die einzelnen Dieser Dekoder hat die Am Eingang CS des Speicherbausteine der Adresse nach anzuordnen. Dekoders (J16/4) liegt entweder das MREQ\*-Signal der CPU, beim System ohne CP/M, oder die ODER Verknüpfung des Banken-Signales mit dem MREQ\*-Signal, beim System mit CP/M (JMP15 Stellung 2). Ist dieses "Veroderte" Signal LOW, so wird der Dekoder aktiviert und damit die Speicher auf der SBC3 angesprochen. Ist das Signal HIGH, werden externe Speicher (ROA64k oder RAM64/256) angesprochen und der Dekoder wird nicht aktiviert; d.h. die Speicher auf der SBC3 werden nicht angesprochen.

B und C Nun zur eigentlichen Dekodierung: Die Eingänge A, (J16/1/2/3) bestimmen, je nach der anliegenden binären Kombination welcher Ausgang aktiviert (LOW) wird. Diese Ausgänge sind jeweils mit dem CS-Eingang der Speicher verbunden. Bei den RAM-Bausteinen hängt noch ein Transistor dazwischen, der aber nur für die Akku-Pufferung benötigt wird. Wird nun auf einen Speicher einer bestimmten Adresse zugegriffen, so wird einer der Ausgänge aktiviert und damit einer der vier Speicher (J6, J7, J8 und J9). Bei Adresse 2000H bis 3FFFH wird z.B. A15 LOW, A14 LOW, A13 HIGH, damit wird der Ausgang 1 (J16/14) aktiviert und damit das 2. EPROM (J7). Da beim CP/M und beim System ohne CP/M verschiedene mit Speicherkonfigurationen der RAM vorliegen, muß der CS Eingang der RAM Bausteine auf verschiedene Ausgänge der Dekoder gelegt werden. Dies geschieht mit JMP12 und JMP13. Sind diese beiden JMP auf Stellung 2, so sind die RAMs von Adresse 4000H bis 5FFFH und 6000H bis 7FFFH. Sind die JMP in Stellung 1, so liegen die RAMs von Adresse 8000H bis 9FFFH und A000H bis BFFFH.

Dekodierung von anderen Speichern

Bisher wurde nur über die Dekodierung von 8k-Speichern gesprochen.

Werden aber andere Speicher (EPROMs: 2732, 27128, 27256; RAMs: 6116)

verwendet, die mehr oder weniger Speicherkapazität als 8k Speicher

haben, so muß die Dekodierung geändert werden. Zu diesem Zweck

wurden die beiden ICs 74 LS 139 (J5 und J13) eingesetzt. In diesen

beiden ICs sind 4 "zwei zu vier Dekoder" enthalten und zwar für

jeden der obengenannten Speicher Typen wird ein solcher Dekoder

verwendet. Auf diese vier Dekoder soll hier nicht näher eingegangen

werden, da sie prinzipiell genauso aufgebaut ist, wie bei 8k

Speichern; mehr zu diesen Speicherkonfigurationen JMP-Stellungen

finden Sie unter 5.3 und folgende).

#### 7.2.7 Akku-Pufferung der RAMs

RAMs sind bekanntlich flüchtige Speicher und haben beim Ausschalten der Versorgungsspannung die negative Eigenschaft ihre Daten zu verlieren. Dies geschieht hier auf der SBC3, dank der Akku-Pufferung, nicht. Beim Ausschalten des Computers versorgt ein Akku (2,4 V und 120 mAh) die RAM-Bausteine mit Strom. Dazu müssen die RAMs aber im "Standby-Mode" sein, d.h. die CS Eingänge der RAMs (J8/20 und J9/20) müssen HIGH sein. Trifft dies zu, sind die RAMs im "Standby-Mode" und benötigen in diesem Zustand mind. 2.0 V Spannung und ca. 0.5 - 2 uA Strom um die Speicherinformation zu halten. Um diesen Standby-Mode sicher zu erreichen, werden schnelle Schalttransistoren zwischen die Dekoderausgänge und den CS-Eingängen der Speicher geschaltet. Fällt nun die Spannung ab, (Ausschalten des Computer, Stromausfall etc.) fällt die Basisspannung ab und die Transistoren sperren. Nun liegt an den CS-Eingängen durch den Akku ein HIGH-Signal. Die beiden 4,7 kOhm Widerstände (R4 und R5) fallen nicht ins Gewicht, da der CS Eingang der Speicher extrem hochohmig

ist. Die Basisspannung der Transistoren wird mit R3 und R6 eingestellt. Die Widerstände R7 und R8 (2,2k) begrenzen den Basisstrom der Transistoren. Diese Begrenzung ist nötig, um die Dekoderausgänge nicht zu stark zu belasten. Die Diode D1 sorgt dafür, daß der Akku bei Spannungsabfall nicht den ganzen Computer mit Strom versorgt. Der Widerstand R9 dient dazu, den Ladestrom für den Akku einzustellen. Durch den eingesetzten Widerstand von 4,7 kohm beträgt der Ladestrom ca. 1 mA. Der Akku hält die Speicherinformation ohne Nachladen bei Zimmertemperatur ca. 1 Jahr. Da der Computer aber sicherlich ab und zu läuft wird der Akku automatisch nachgeladen. Um den Akku voll aufzuladen, benötigt man bei einem eingestellten Ladestrom von 1 mA (R9 = 4,7 kohm) ca. 120 Stunden. Der Akku kann also normalerweise nicht leer werden. Verwenden Sie 2k RAMs müssen Sie darauf achten, daß Sie CMOS RAMs benutzen, andernfalls ist der Akku innerhalb einiger Stunden leer. Verwenden Sie die mitgelieferten 8k RAMs oder andere 8k RAMs brauchen Sie sich diesbezüglich keine Sorgen machen, da es nur CMOS 8k RAMs gibt.

#### 7.2.8 Speicher

Wie unter 5.3 und folgende schon erläutert sind 6 verschiedene Speichertypen möglich. Die Baugruppe hat eine Grundeinstellung, die 8k Speicher vorsieht (EPROM 2764 und RAM 6264). Die vier verschiedenen einsetzbaren EPROM-Typen sind bis auf Pin 26 und 27 Pinkompatibel. Um Pinkompatibilität zu erreichen werden diese beiden Pins über JMP4 und JMP3 so eingestellt, daß die jeweiligen Speicher gesteckt werden können. Die beiden RAM-Typen sind bis auf Pin 23 Pinkompatibel. Hier wird mit JMP2 die verschiedene Pinbelegung ausgeglichen. Mögliche Speicherkonfigurationen siehe unter 5.3 und folgende.

#### 7.2.9 Die CPU (Central Processing Unit) Z80

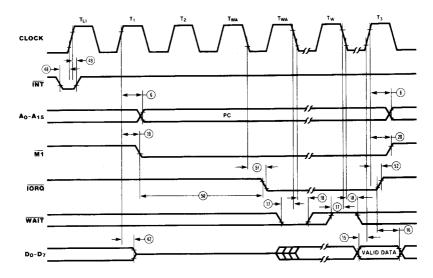

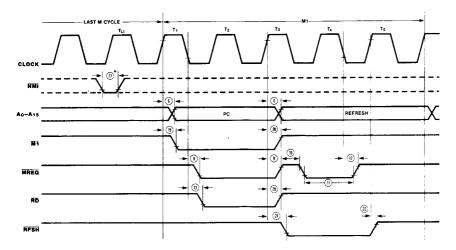

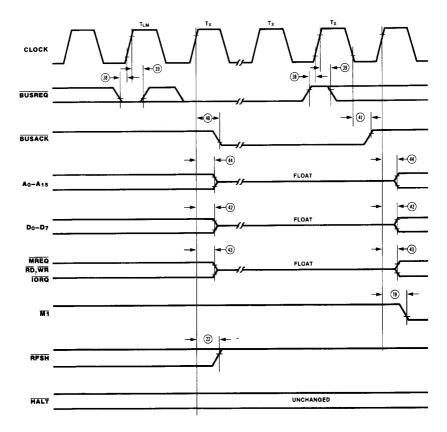

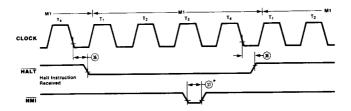

Siehe Datenblatt CPU Z80 (unter 10. Bauelemente)

#### 8. Anwendungsbeispiele

- 8.1 Einsatz im Einsteigerpaket (siehe unter 5.3.1)

- 8.2 Einsatz im System mit Bildschirm und Tastatur ohne CP/M (siehe unter 5.3.1)

- 8.3 Professionelles System mit CP/M (siehe unter 5.3.2)

- 8.4 CP/M-System mit Christiani ZEAT (siehe unter 5.3.3)

#### 9. Ausblick, Diverses

Falls irgendwelche Änderungen auf dieser Baugruppe auftreten, erfahren Sie diese durch die Zeitschrift LOOP (siehe unter Punkt 11).

Bitte senden Sie uns die dem Bausatz oder Fertiggerät beiliegende Kritikkarte ausgefüllt zurück, denn nur so können wir Fehler oder Mißverständnisse irgendwelcher Art erkennen und verbessern! Vielen Dank schon im Voraus für Ihre Hilfe!

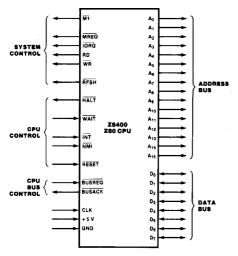

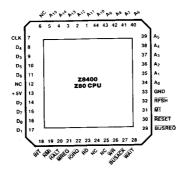

### Z8400 Z80<sup>®</sup> CPU Central Processing Unit

# Zilog

#### Product Specification

April 1985

#### **FEATURES**

- The instruction set contains 158 instructions. The 78 instructions of the 8080A are included as a subset; 8080A software compatibility is maintained.

- Eight MHz, 6 MHz, 4 MHz, and 2.5 MHz clocks for the Z80H, Z80B, Z80A, and Z80 CPU result in rapid instruction execution with consequent high data throughput.

- The extensive instruction set includes string, bit, byte, and word operations. Block searches and block transfers, together with indexed and relative addressing, result in the most powerful data handling capabilities in the microcomputer industry.

- The Z80 microprocessors and associated family of peripheral controllers are linked by a vectored interrupt

- system. This system may be daisy-chained to allow implementation of a priority interrupt scheme. Little, if any, additional logic is required for daisy-chaining.

- Duplicate sets of both general-purpose and flag registers are provided, easing the design and operation of system software through single-context switching, background-foreground programming, and single-level interrupt processing. In addition, two 16-bit index registers facilitate program processing of tables and arrays.

- There are three modes of high speed interrupt processing: 8080 similar, non-Z80 peripheral device, and Z80 Family peripheral with or without daisy chain.

- On-chip dynamic memory refresh counter.

Figure 1. Pin Functions

Figure 2a. 40-Pin Dual-In-Line Package (DIP)

Pin Assignments

Figure 2b. 44-Pin Chip Carrier Pin Assignments

#### **GENERAL DESCRIPTION**

The Z80, Z80A, Z80B, and Z80H CPUs are third-generation single-chip microprocessors with exceptional computational power. They offer higher system throughput and more efficient memory utilization than comparable second- and third-generation microprocessors. The internal registers contain 208 bits of read/write memory that are accessible to the programmer. These registers include two sets of six general-purpose registers which may be used individually as either 8-bit registers or as 16-bit register pairs. In addition, there are two sets of accumulator and flag registers. A group of "Exchange" instructions makes either set of main or alternate registers accessible to the programmer. The alternate set allows operation in foreground-background mode or it may be reserved for very fast interrupt response.

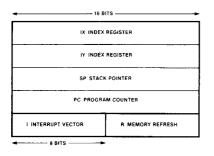

The Z80 also contains a Stack Pointer, Program Counter, two index registers, a Refresh register (counter), and an Interrupt register. The CPU is easy to incorporate into a system since it requires only a single +5V power source. All output signals are fully decoded and timed to control standard memory or peripheral circuits; the CPU is supported by an extensive family of peripheral controllers. The internal block diagram (Figure 3) shows the primary functions of the Z80 processors. Subsequent text provides more detail on the Z80 I/O controller family, registers, instruction set, interrupts and daisy chaining, and CPU timing.

Figure 3. Z80 CPU Block Diagram

#### **Z80 MICROPROCESSOR FAMILY**

The Zilog Z80 microprocessor is the central element of a comprehensive microprocessor product family. This family works together in most applications with minimum requirements for additional logic, facilitating the design of efficient and cost-effective microcomputer-based systems.

Zilog has designed five components to provide extensive support for the Z80 microprocessor. These are:

- The PIO (Parallel Input/Output) operates in both data-byte I/O transfer mode (with handshaking) and in bit mode (without handshaking). The PIO may be configured to interface with standard parallel peripheral devices such as printers, tape punches, and keyboards.

- The CTC (Counter/Timer Circuit) features four programmable 8-bit counter/timers, each of which has an

- 8-bit prescaler. Each, of the four channels may be configured to operate in either counter or timer mode.

- The DMA (Direct Memory Access) controller provides dual port data transfer operations and the ability to terminate data transfer as a result of a pattern match.

- The SIO (Serial Input/Output) controller offers two channels. It is capable of operating in a variety of programmable modes for both synchronous and asynchronous communication, including Bi-Synch and SDLC.

- The DART (Dual Asynchronous Receiver/Transmitter) device provides low cost asynchronous serial communication. It has two channels and a full modem control interface.

#### **Z80 CPU REGISTERS**

- 8 BITS -

Figure 4 shows three groups of registers within the Z80 CPU. The first group consists of duplicate sets of 8-bit registers: a principal set and an alternate set (designated by '[prime], e.g., A'). Both sets consist of the Accumulator Register, the Flag Register, and six general-purpose registers. Transfer of data between these duplicate sets of registers is accomplished by use of "Exchange" instructions. The result is faster response to interrupts and easy. efficient implementation of such versatile pro-

gramming techniques as background-foreground data processing. The second set of registers consists of six registers with assigned functions. These are the I (Interrupt Register), the R (Refresh Register), the IX and IY (Index Registers), the SP (Stack Pointer), and the PC (Program Counter). The third group consists of two interrupt status flip-flops, plus an additional pair of flip-flops which assists in identifying the interrupt mode at any particular time. Table 1 provides further information on these registers.

#### MAIN REGISTER SET

#### ALTERNATE REGISTER SET

| A ACCUMULATOR     | F FLAG REGISTER   | A. ACCUMULATOR     | F' FLAG REGISTER   |

|-------------------|-------------------|--------------------|--------------------|

| B GENERAL PURPOSE | C GENERAL PURPOSE | B' GENERAL PURPOSE | C' GENERAL PURPOSE |

| D GENERAL PURPOSE | E GENERAL PURPOSE | D' GENERAL PURPOSE | E' GENERAL PURPOSE |

| H GENERAL PURPOSE | L GENERAL PURPOSE | H' GENERAL PURPOSE | L' GENERAL PURPOSE |

Figure 4. CPU Registers

#### **ZRO CPU REGISTERS** (Continued)

Table 1. Z80 CPU Registers

| F                                  | Register           | Size (Bits) | Remarks                                                                                                                                              |  |

|------------------------------------|--------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A, A'                              | Accumulator        | 8           | Stores an operand or the results of an operation.                                                                                                    |  |

| F, F'                              | Flags              | 8           | See Instruction Set.                                                                                                                                 |  |

| B, B'                              | General Purpose    | 8           | Can be used separately or as a 16-bit register with C.                                                                                               |  |

| C, C'                              | General Purpose    | 8           | See B, above.                                                                                                                                        |  |

| D, D'                              | General Purpose    | 8           | Can be used separately or as a 16-bit register with E.                                                                                               |  |

| E. E'                              | General Purpose    | 8           | See D, above.                                                                                                                                        |  |

| H. H'                              | General Purpose    | 8           | Can be used separately or as a 16-bit register with L.                                                                                               |  |

| L, L'                              | General Purpose    | 8           | See H, above.                                                                                                                                        |  |

|                                    |                    |             | Note: The (B,C). (D,E), and (H,L) sets are combined as follows:  B — High byte C — Low byte  D — High byte E — Low byte  H — High byte L — Low byte  |  |

| 1                                  | Interrupt Register | 8           | Stores upper eight bits of memory address for vectored interrupt processing.                                                                         |  |

| R                                  | Refresh Register   | 8           | Provides user-transparent dynamic memory refresh. Automatically<br>incremented and placed on the address bus during each<br>instruction fetch cycle. |  |

| iX                                 | Index Register     | 16          | Used for indexed addressing.                                                                                                                         |  |

| IY                                 | Index Register     | 16          | Used for indexed addressing                                                                                                                          |  |

| SP                                 | Stack Pointer      | 16          | Holds address of the top of the stack. See Push or Pop in instruction set.                                                                           |  |

| PC                                 | Program Counter    | 16          | Holds address of next instruction.                                                                                                                   |  |

| IFF <sub>1</sub> -IFF <sub>2</sub> | Interrupt Enable   | Flip-Flops  | Set or reset to indicate interrupt status (see Figure 4).                                                                                            |  |

| IMFa-IMFb                          | Interrupt Mode     | Flip-Flops  | Reflect Interrupt mode (see Figure 4).                                                                                                               |  |

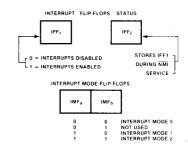

#### INTERRUPTS: GENERAL OPERATION

The CPU accepts two interrupt input signals:  $\overline{\text{NM}}$  and  $\overline{\text{INT}}$ . The  $\overline{\text{NM}}$  is a non-maskable interrupt and has the highest priority.  $\overline{\text{INT}}$  is a lower priority interrupt and it requires that interrupts be enabled in software in order to operate.  $\overline{\text{INT}}$  can be connected to multiple peripheral devices in a wired-OR configuration.

The Z80 has a single response mode for interrupt service for the non-maskable interrupt. The maskable interrupt,  $\overline{\text{INT}}$ , has three programmable response modes available. These are:

- Mode 0 similar to the 8080 microprocessor.

- Mode 1 Peripheral Interrupt service, for use with non-8080/Z80 systems.

- Mode 2 a vectored interrupt scheme, usually daisy-chained, for use with Z80 Family and compatible peripheral devices.

The CPU services interrupts by sampling the  $\overline{\text{NM}}$  and  $\overline{\text{INT}}$  signals at the rising edge of the last clock of an instruction. Further interrupt service processing depends upon the type of interrupt that was detected. Details on interrupt responses are shown in the CPU Timing Section.

Non-Maskable Interrupt (NMI). The nonmaskable interrupt cannot be disabled by program control and therefore will be accepted at all times by the CPU. NMI is usually reserved for servicing only the highest priority type interrupts, such as that for orderly shutdown after power failure has been detected. After recognition of the NMI signal (providing BUSREQ is not active), the CPU jumps to restart location 0066H. Normally, software starting at this address contains the interrupt service routine.

Maskable Interrupt (INT). Regardless of the interrupt mode set by the user, the Z80 response to a maskable interrupt input follows a common timing cycle. After the

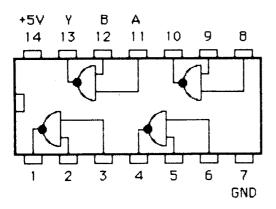

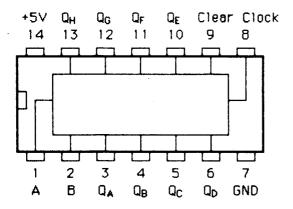

# 74LS273

8-Bit D-Register mit Clear

# Logiktabelle:

|   | · INPUT |          |   | OUTPUT |

|---|---------|----------|---|--------|

| 1 | CLEAR   | CLOCK    | D | Q      |

|   | L       | ×        | × | L      |

|   | Н       | <b>†</b> | Н | Н      |

|   | Н       | †        | L | l L    |

| ı | Н       | L        | L | QO     |

positive Logik

Typ. Impuls-

Verzögerungszeit: 17,5 ns

Typ Versor-

gungsstrom: 17,5 mA

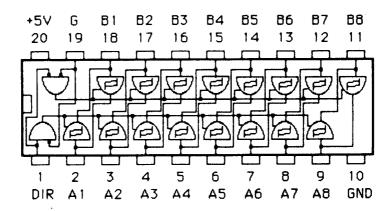

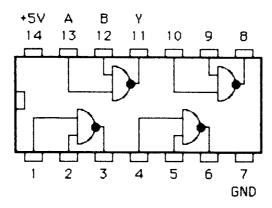

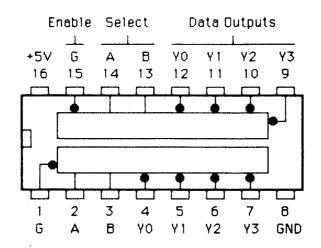

# 74LS245

Acht Bus-Transceiver (Tri-State)

# Logiktabelle:

|   | Enable<br>G | Direktion<br>DIR | Operation       |

|---|-------------|------------------|-----------------|

|   | L           | L                | B data to A Bus |

|   | L           | н                | A data to B Bus |

|   | н           | ×                | isolation       |

| ı |             |                  |                 |

Typ. Impuls-Verzögerungszeit: 8 ns

Typ. Versor-gungsstrom:

62 mA

#### 8-BIT LOAD GROUP (Continued)

|                | Symbolic     |          |    |   | Fla | ags |     |   |   |    | Opcod               | le  |     | No. of | No. of M | No. of T |          |

|----------------|--------------|----------|----|---|-----|-----|-----|---|---|----|---------------------|-----|-----|--------|----------|----------|----------|

| Mnemonic       | Operation    | s        | Z  |   | Н   |     | P/V | N | С |    | 543                 |     | Hex | Bytes  | Cycles   | States   | Comments |

| LD (IY + d), n | (IY + d) ← n | •        |    | Х |     | Х   |     |   | • | 11 | 111                 | 101 | FD  | 4      | 5        | 19       |          |

|                |              |          |    |   |     |     |     |   |   | 00 | 110                 | 110 | 36  |        |          |          |          |

|                |              |          |    |   |     |     |     |   |   |    | <b>←</b> d <b>→</b> | •   |     |        |          |          |          |

|                |              |          |    |   |     |     |     |   |   |    | <b>←</b> n →        | •   |     |        |          |          |          |

| D A, (BC)      | A ← (BC)     | •        | •  | Х | •   | Х   | •   | ٠ | • | 00 | 001                 | 010 | 0A  | 1      | 2        | 7        |          |

| _D A, (DE)     | A ← (DE)     | •        | ٠  | Χ | ٠   | Х   | •   | • | ٠ | 00 | 011                 | 010 | 1A  | 1      | 2        | 7        |          |

| _D A, (nn)     | A ← (nn) .   | •        | •  | Χ | ٠   | Χ   | •   | ٠ | • | 00 | 111                 | 010 | ЗА  | 3      | 4        | 13       |          |

|                |              |          |    |   |     |     |     |   |   |    | <b>←</b> n →        | •   |     |        |          |          |          |

|                |              |          |    |   |     |     |     |   |   |    | <b>←</b> n →        | •   |     |        |          |          |          |

| _D (BC), A     | (BC) ← A     | •        | •  | Х | •   | Χ   | •   | • | • | 00 | 000                 | 010 | 02  | 1      | 2        | 7        |          |

| .D (DE), A     | (DE) ← A     | •        | ٠  | Х | ٠   | Χ   | •   | • | • | 00 | 010                 | 010 | 12  | 1      | 2        | 7        |          |

| _D (nn), A     | (nn) ← A     | •        | ٠  | Х | ٠   | Х   | •   | • | • | 00 | 110                 | 010 | 32  | 3      | 4        | 13       |          |

|                |              |          |    |   |     |     |     |   |   |    | <b>←</b> n →        | •   |     |        |          |          |          |

|                |              |          |    |   |     |     |     |   |   |    | <b>←</b> n →        | •   |     |        |          |          |          |

| _D A, I        | A ← I        | ‡        | \$ | Х | 0   | Х   | IFF | 0 | ٠ | 11 | 101                 | 101 | ED  | 2      | 2        | 9        |          |

|                |              |          |    |   |     |     |     |   |   | 01 | 010                 | 111 | 57  |        |          |          |          |

| DA, R          | A ← R        | <b>‡</b> | \$ | Х | 0   | Х   | IFF | 0 | • | 11 | 101                 | 101 | ED  | 2      | 2        | 9        |          |

|                |              |          |    |   |     |     |     |   |   | 01 | 011                 | 111 | 5F  |        |          |          |          |

| DI, A          | I ← A        | •        | •  | X | •   | Χ   | •   | • | • | 11 | 101                 | 101 | ED  | 2      | 2        | 9        |          |

|                |              |          |    |   |     |     |     |   |   | 01 | 000                 | 111 | 47  |        |          |          |          |

| _DR, A         | R←A          | •        | ٠  | Х | •   | Х   | •   | • | • | 11 | 101                 | 101 | ED  | 2      | 2        | 9        |          |

|                |              |          |    |   |     |     |     |   |   | 01 | 001                 | 111 | 4F  |        |          |          |          |

NOTE: IFF, the content of the interrupt enable flip-flop, (IFF<sub>2</sub>), is copied into the P/V flag.

#### **16-BIT LOAD GROUP**

| Mnemonic    | Symbolic<br>Operation      | s | z |   |   | ıgs |   | N | С |    | Opcod<br>543        |     | Hex | No. of<br>Bytes | No. of M<br>Cycles | No. of T<br>States | Con | ments |

|-------------|----------------------------|---|---|---|---|-----|---|---|---|----|---------------------|-----|-----|-----------------|--------------------|--------------------|-----|-------|

| LD dd, nn   | dd ← nn                    | • |   | Х | • | Х   | • | • |   | 00 | dd0                 | 001 |     | 3               | 3                  | 10                 | dd  | Pair  |

|             |                            |   |   |   |   |     |   |   |   |    | <b>←</b> n →        |     |     |                 |                    |                    | 00  | BC    |

|             |                            |   |   |   |   |     |   |   |   |    | ← n →               |     |     |                 |                    |                    | 01  | DE    |

| LD IX, nn   | IX ← nn                    | ٠ | ٠ | Х | • | Х   | • | ٠ | • | 11 | 011                 | 101 | DD  | 4               | 4                  | 14                 | 10  | HL    |

|             |                            |   |   |   |   |     |   |   |   | 00 | 100                 | 001 | 21  |                 |                    |                    | 11  | SP    |

|             |                            |   |   |   |   |     |   |   |   |    | <b>←</b> n →        |     |     |                 |                    |                    |     |       |

|             |                            |   |   |   |   |     |   |   |   |    | ← n →               |     |     |                 |                    |                    |     |       |

| LD IY, nn   | IY ← nn                    | • | • | Х | • | Х   | ٠ | • | • | 11 | 111                 | 101 | FD  | 4               | 4                  | 14                 |     |       |

|             |                            |   |   |   |   |     |   |   |   | 00 | 100                 | 001 | 21  |                 |                    |                    |     |       |

|             |                            |   |   |   |   |     |   |   |   |    | ← n →               |     |     |                 |                    |                    |     |       |

|             |                            |   |   |   |   |     |   |   |   |    | ← n →               |     |     |                 |                    |                    |     |       |

| LD HL, (nn) | H ← (nn + 1)               | • | • | Х | • | Х   | • | • | ٠ | 00 | 101                 | 010 | 2A  | 3               | 5                  | 16                 |     |       |

|             | L ← (nn)                   |   |   |   |   |     |   |   |   |    | <b>←</b> n→         |     |     |                 |                    |                    |     |       |

|             |                            |   |   |   |   |     |   |   |   |    | <b>←</b> n <b>→</b> |     |     |                 |                    |                    |     |       |

| LD dd. (nn) | dd <sub>H</sub> ← (nn + 1) | • | • | Х | • | Х   | • | • | • | 11 | 101                 | 101 | ED  | 4               | 6                  | 20                 |     |       |

|             | dd <sub>L</sub> ← (nn)     |   |   |   |   |     |   |   |   | 01 | dd1                 | 011 |     |                 |                    |                    |     |       |

|             |                            |   |   |   |   |     |   |   |   |    | ← n →               |     |     |                 |                    |                    |     |       |

|             |                            |   |   |   |   |     |   |   |   |    | <b>←</b> n →        |     |     |                 |                    |                    |     |       |

NOTE:  $(PAIR)_H$ ,  $(PAIR)_L$  refer to high order and low order eight bits of the register pair respectively, e.g.,  $BC_L = C$ ,  $AF_H = A$ .

#### 16-BIT LOAD GROUP (Continued)

| Mnemonic     | Symbolic<br>Operation      | s | z |   | Fla<br>H | ıgs | P/V | N | С | 76 | Opcod<br>543        | e<br>210 | Hex      | No. of<br>Bytes | No. of M<br>Cycles | No. of T<br>States | Comr | nents |

|--------------|----------------------------|---|---|---|----------|-----|-----|---|---|----|---------------------|----------|----------|-----------------|--------------------|--------------------|------|-------|

| _D IX, (nn)  | IX <sub>H</sub> ← (nn + 1) | • |   | Х | •        | X   | •   | • | • | 11 | 011                 | 101      | DD       | 4               | 6                  | 20                 |      |       |

| ()           | iX <sub>L</sub> ← (nn)     |   |   |   |          |     |     |   |   | 00 | 101                 | 010      | 2A       |                 |                    |                    |      |       |

|              |                            |   |   |   |          |     |     |   |   |    | <b>←</b> n →        |          |          |                 |                    |                    |      |       |

|              |                            |   |   |   |          |     |     |   |   |    | <b>←</b> n →        |          |          |                 | _                  |                    |      |       |

| DIY, (nn)    | IY <sub>H</sub> ← (nn + 1) | • | • | X | •        | Х   | •   | • | • | 11 | 111                 |          | FD       | 4               | 6                  | 20                 |      |       |

|              | IY <sub>L</sub> ← (nn)     |   |   |   |          |     |     |   |   | 00 | 101                 |          | 2A       |                 |                    |                    |      |       |

|              |                            |   |   |   |          |     |     |   |   |    | ← n →               |          |          |                 |                    |                    |      |       |

| 0 (> 111     | ( 1 4) H                   | _ | _ | v |          | Х   |     |   |   | 00 | 100                 |          | 22       | 3               | 5                  | 16                 |      |       |

| _D (nn), HL  | (nn + 1), ← H              | • | ٠ | Х | •        | ^   | •   | • | • | 00 | + n →               |          | 22       | Ü               | Ü                  |                    |      |       |

|              | (nn) <del>←</del> L        |   |   |   |          |     |     |   |   |    | + n →               |          |          |                 |                    |                    |      |       |

| LD (nn), dd  | (nn + 1) ← dd <sub>H</sub> |   |   | x |          | Х   |     |   |   | 11 |                     | 101      | ED       | 4               | 6                  | 20                 |      |       |

| ED (rin), dd | (nn) ← dd <sub>i</sub>     |   |   |   |          |     |     |   |   | 01 |                     | 011      |          |                 |                    |                    |      |       |

|              | () 33                      |   |   |   |          |     |     |   |   |    | ← n →               |          |          |                 |                    |                    |      |       |

|              |                            |   |   |   |          |     |     |   |   |    | <b>←</b> n →        |          |          |                 |                    |                    |      |       |

| LD (nn), IX  | (nn + 1) ← IX <sub>H</sub> |   | • | Х | •        | Χ   | ٠   | • | • | 11 | 011                 | 101      | DD       | 4               | 6                  | 20                 |      |       |

| \ /-         | (nn) ← iX <sub>L</sub>     |   |   |   |          |     |     |   |   | 00 | 100                 | 010      | 22       |                 |                    |                    |      |       |