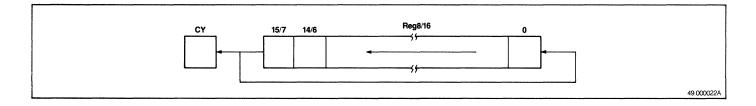

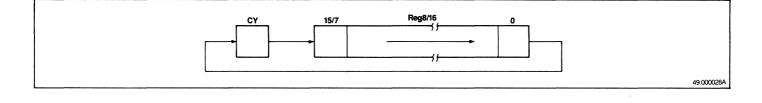

# **NEC Electronics Inc.**

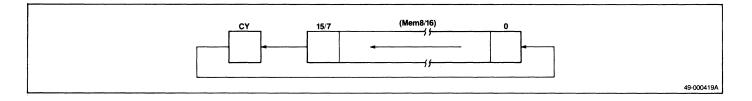

USER'S MANUAL

## October 1986

# μ**PD70108 (V20™)** 8/16-Bit CMOS Microprocessor

# μ**PD70116 (V30™)** 16-Bit CMOS Microprocessor

# μ**PD70108 (V20)** 8/16-Bit CMOS Microprocessor

## μ**PD70116 (V30)** 16-Bit CMOS Microprocessor

October 1986 Stock No. 500350 ©1986 NEC Electronics Inc./Printed in U.S.A.

# **NEC Electronics Inc.**

## CONTENTS

| Se | cti | on |

|----|-----|----|

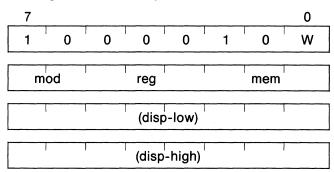

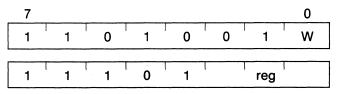

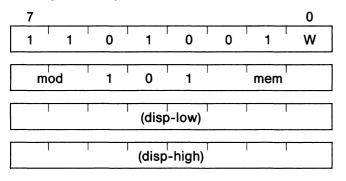

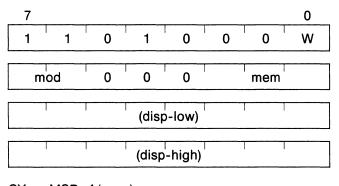

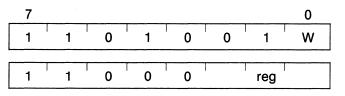

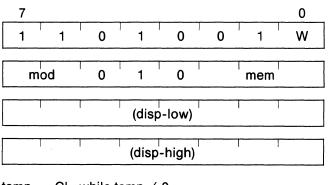

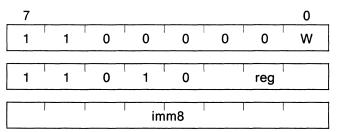

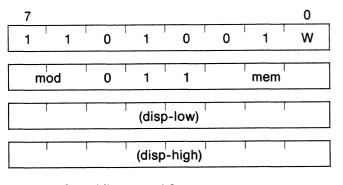

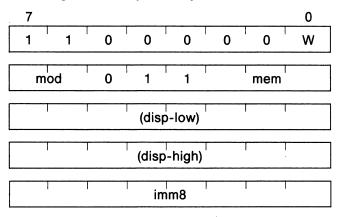

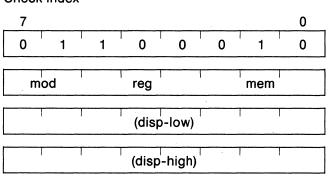

|----|-----|----|

| 1   | Introduction                         | 1-1         |

|-----|--------------------------------------|-------------|

| 2   | Pin Description                      | 2-1         |

| 3   | Functional Description               | 3-1         |

|     | Execution Unit (EXU)                 | 3-1         |

|     | Bus Control Unit (BCU)               | 3-4         |

| 4   | Memory and I/O Configuration         | 4-1         |

|     | Memory Configuration                 | 4-1         |

|     | Memory Accessing                     | 4-2         |

|     | I/O Configuration and Accessing      | 4-3         |

| 5   | Read/Write Timing                    | 5-1         |

| 6   | Interrupts                           | 6-1         |

|     | Maskable Interrupts                  | 6-2         |

|     | BRK Flag (Single-Step Interrupt)     | 6-3         |

|     | Interrupt Disable Timing             | 6-4         |

|     | Interrupts During Block Instructions | 6-4         |

| 7   | Reset Operation                      | 7-1         |

| . 8 | Native and $\mu$ PD8080AF            |             |

| Ū   | Emulation Modes                      | 8-1         |

|     | Native and 8080 Mode Shifting        | 8-1         |

|     | Native to 8080 Emulation Mode        | 8-2         |

| 9   | Standby Mode                         | 0-2<br>9-1  |

| 3   | Entering Standby Mode                | 9-1<br>9-1  |

|     | Status Signals in Standby Mode       | 9-1<br>9-1  |

|     | Exiting Standby Mode by              | 9-1         |

|     | External Interrupts                  | 9-1         |

|     | Exiting Standby Mode                 | 9-1         |

|     | by Reset                             | 9-1         |

| 10  | Logical and Physical Addresses       | 9-1<br>10-1 |

| 10  | Physical Address Generation          | 10-1        |

|     | Memory Segments                      | 10-1        |

| 11  | Addressing Modes                     | 10-1        |

| 11  | Instruction Address                  | 11-1        |

|     | Memory Operand Address               | 11-2        |

| 12  | Instruction Set                      | 12-1        |

| 12  |                                      |             |

|     | Data Transfer                        | 12-4        |

|     | Repeat Prefixes                      | 12-14       |

|     | Primitive Block Transfer             | 12-16       |

|     | Bit Field Manipulation               | 12-21       |

|     | Input/Output                         | 12-25       |

|     | Primitive Input/Output               | 12-28       |

|     | Addition/Subtraction                 | 12-29       |

|     | BCD Arithmetic                       | 12-42       |

|     | Increment/Decrement                  | 12-47       |

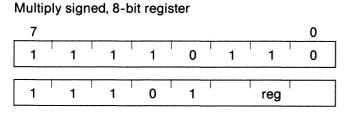

|     | Multiplication                       | 12-50       |

|     | Division                             | 12-56       |

|     | BCD Adjust                           | 12-61       |

|     | Data Conversion                      | 12-63       |

|     | Comparison                           | 12-65       |

|     | Complement Operation                 | 12-68       |

|     | Logical Operation                    | 12-70       |

|     | Bit Manipulation                     | 12-81       |

|     | Shift                                | 12-100      |

|     | Rotate                               | 12-118      |

| 12   | Instruction Set (cont)               |        |

|------|--------------------------------------|--------|

|      | Subroutine Control                   | 12-142 |

|      | Stack Operation                      | 12-146 |

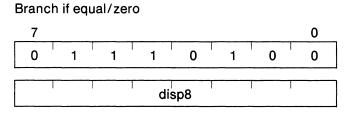

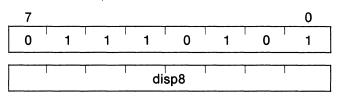

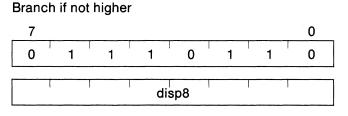

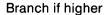

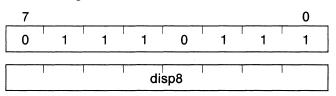

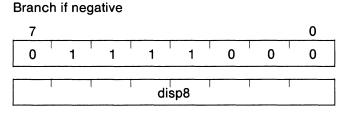

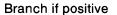

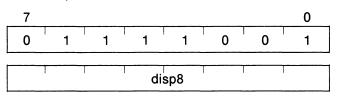

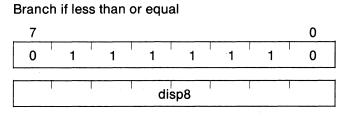

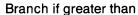

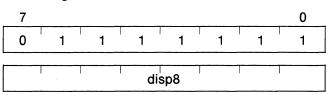

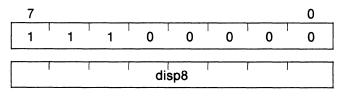

|      | Branch                               | 12-154 |

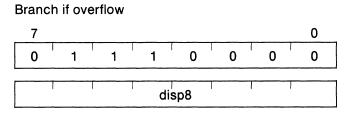

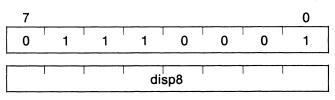

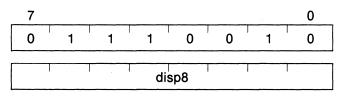

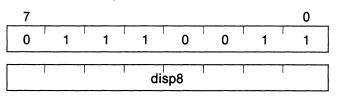

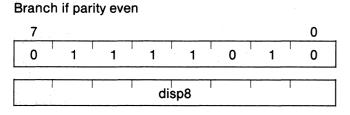

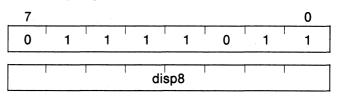

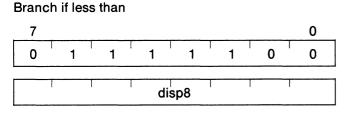

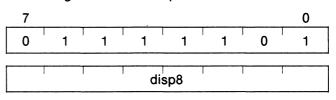

|      | Conditional Branch                   | 12-157 |

|      | Break                                | 12-167 |

|      | CPU Control                          | 12-171 |

|      | Segment Override Prefix              | 12-176 |

|      | Emulation Mode                       | 12-176 |

| Арр  | endix                                |        |

| A    | μPD70108/70116 Instruction Index     | A-1    |

| Tabl |                                      |        |

| 1-1  | μPD70108/70116 Pin Identification    | 1-2    |

| 4-1  | Data Type and Addressing             | 4-1    |

| 6-1  | Interrupt Sources                    | 6-1    |

| 9-1  | Signal Status in Standby Mode        | 9-1    |

| 12-1 | Operand Types                        | 12-1   |

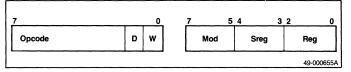

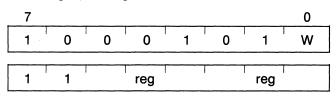

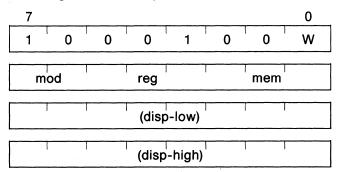

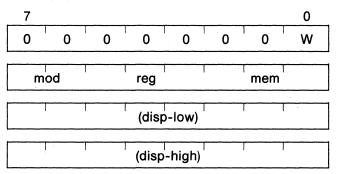

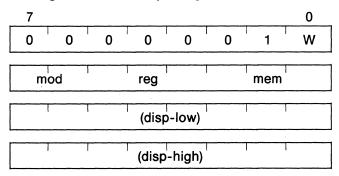

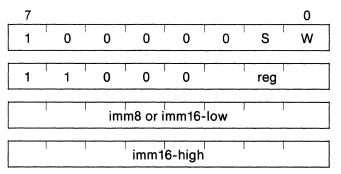

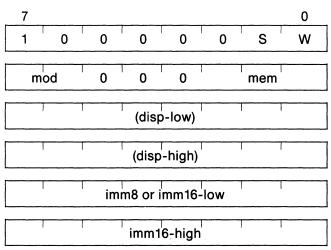

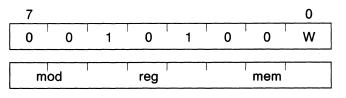

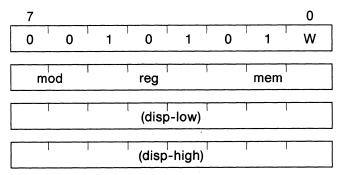

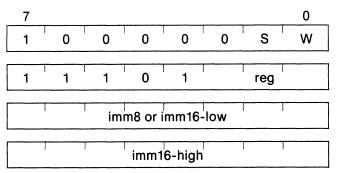

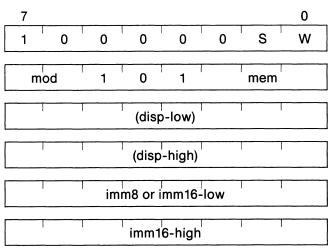

|      | Instruction Words                    | 12-2   |

| 12-3 | Operation Description                | 12-2   |

|      | Flag Operations                      | 12-3   |

| 12-5 | Memory Addressing                    | 12-3   |

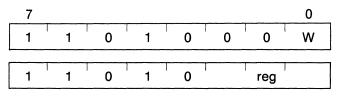

| 12-6 | Selection of 8- and 16-Bit Registers | 12-3   |

| 12-7 | Selection of 8-Bit and               |        |

|      | Segment Register                     | 12-3   |

| Figu | re                                   |        |

| 1-1  | µPD70108/70116 Simplified Block      |        |

|      | Diagram                              | 1-1    |

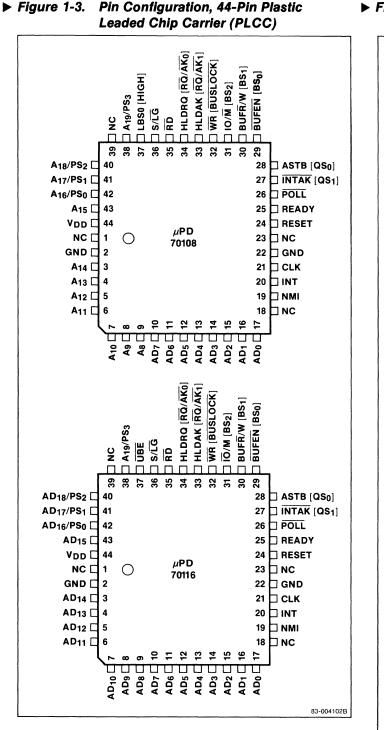

| 1-2  | Pin Configuration,                   |        |

|      | 40-Pin Plastic or Ceramic DIP        | 1-2    |

| 1-3  | Pin Configuration,                   |        |

|      | 44-Pin PLCC                          | 1-3    |

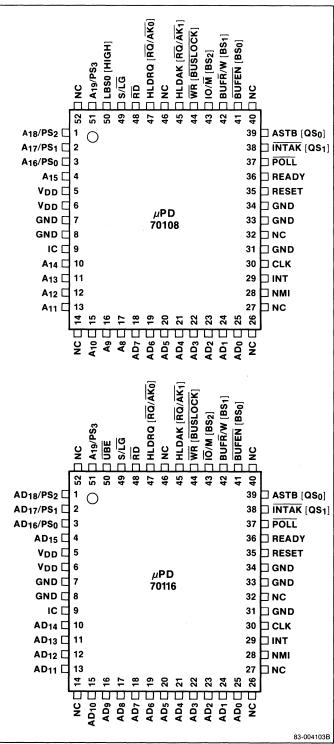

| 1-4  | Pin Configuration,                   |        |

|      | 52-Pin Plastic Miniflat              | 1-3    |

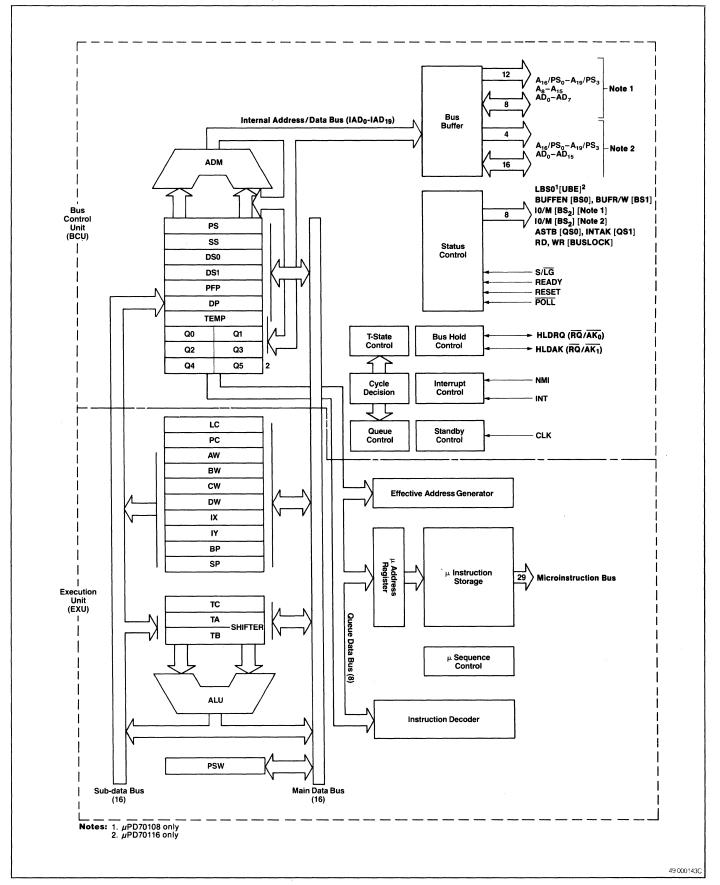

| 3-1  | μPD70108/70116 Block Diagram         | 3-2    |

| 3-2  | Effective Address Generator          | 3-3    |

| 4-1  | Memory Map                           | 4-1    |

| 4-2  | Word and Double Word Placement       |        |

|      | in Memory                            | 4-1    |

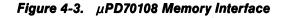

| 4-3  | µPD70108 Memory Interface            | 4-2    |

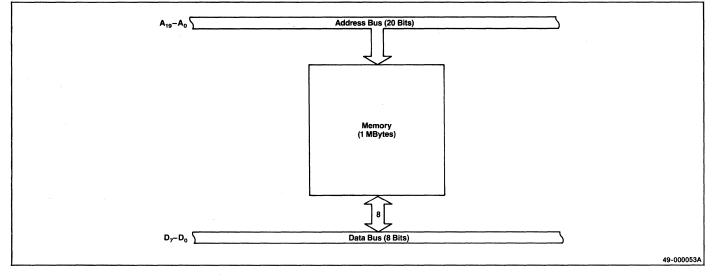

| 4-4  | µPD70116 Memory Interface            | 4-2    |

| 4-5  | I/O Map                              | 4-3    |

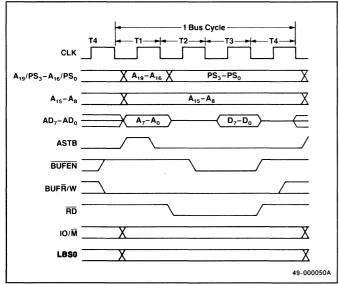

| 5-1  | Read Timing of $\mu$ PD70108 Memory  |        |

|      | and I/O (Small-Scale Systems)        | 5-1    |

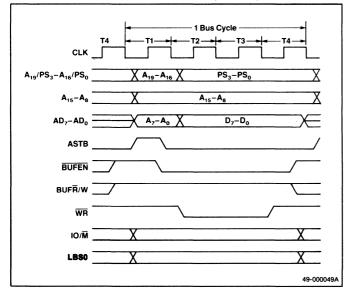

| 5-2  | Write Timing of µPD70108 Memory      |        |

|      | and I/O (Small-Scale Systems)        | 5-1    |

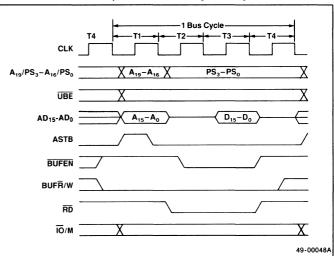

| 5-3  | Read Timing of $\mu$ PD70116 Memory  |        |

|      | and I/O (Small-Scale Systems)        | 5-1    |

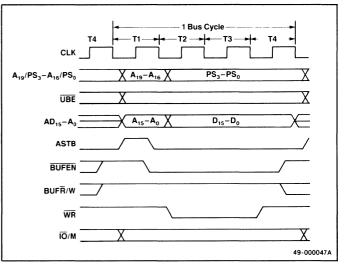

| 5-4  | Write Timing of $\mu$ PD70116 Memory |        |

|      | and I/O (Small-Scale Systems)        | 5-1    |

## **NEC Electronics Inc.**

## **CONTENTS** (cont)

| Figu | Ire                                  | Page | Figu | re                             | Page |

|------|--------------------------------------|------|------|--------------------------------|------|

| 5-5  | Read Timing of $\mu$ PD70108 Memory  |      | 8-1  | Corresponding Registers        | 8-1  |

|      | and I/O (Large-Scale Systems)        | 5-2  | 8-2  | Corresponding PSW and Flags    | 8-1  |

| 5-6  | Write Timing of $\mu$ PD70108 Memory |      | 8-3  | Mode Shift Operation of CPU    | 8-2  |

|      | and I/O (Large-Scale Systems)        | 5-2  |      | Shift from Native to 8080 Mode |      |

| 5-7  | Read Timing of $\mu$ PD70116 Memory  |      |      | Using BRKEM Instruction        | 8-3  |

|      | and I/O (Large-Scale Systems)        | 5-2  | 8-5  | Shift from Native to 8080 Mode |      |

| 5-8  | Write Timing of $\mu$ PD70116 Memory |      |      | Using RETI Instruction         | 8-3  |

|      | and I/O (Large-Scale Systems)        | 5-2  | 8-6  | Shift from 8080 to Native Mode |      |

| 6-1  | Interrupt Vector Table               | 6-1  |      | Using NMI, INT, and            |      |

|      | µPD70108 Interrupt Acknowledge       |      |      | CALLN Instruction              | 8-4  |

|      | Timing                               | 6-2  | 8-6  | Shift from 8080 to Native Mode |      |

| 6-3  | µPD70116 Interrupt Acknowledge       |      |      | Using RETEM Instruction        | 8-5  |

|      | Timing                               | 6-2  | 10-1 | Physical Addressing            | 10-1 |

## **Revision History**

Aug 1985 Original Issue

Sep 1986 Table 1-1 revised, figures 1-3 and 1-4 added, Section 2 revised and rearranged. Marginal arrows (▶) identify significant changes in Sections 1, 2, and 12.

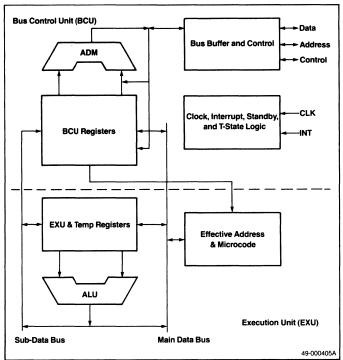

## Description

The  $\mu$ PD70108 (V20) and  $\mu$ PD70116 (V30) are highperformance, low-power CMOS microprocessors with a 16-bit internal architecture. The  $\mu$ PD70108 has an 8-bit external data bus and the  $\mu$ PD70116 has a 16-bit external data bus. Figure 1 is a simplified block diagram.

The  $\mu$ PD70108/70116 has a powerful instruction set that is a superset of the  $\mu$ PD8086/8088 instruction set and provides the following enhanced operations:

- Multidigit BCD addition, subtraction, comparison of 1- to 254-digit BCD strings

- High-speed multiplication/division

- Bit field manipulations

- Data transfer of 1- to 16-bit fields between memory and accumulator

- Bit manipulation instructions

- 8- or 16-bit register/memory operands

Set, clear, invert, or test any bit

Dedicated hardware performs high-speed multiplication/division (4 to 6  $\mu$ s at 8 MHz) and effective address calculation. In addition, an internal dual bus system reduces processing time.

The  $\mu$ PD70108/70116 has three operating modes: native, emulation, and standby. Native mode executes the  $\mu$ PD70108/70116 instruction set; emulation mode directly executes the  $\mu$ PD8080AF instruction set. The standby mode significantly reduces power consumption.

## Features

- □ 101 instructions

- □ 250-ns instruction execution time (8-MHz clock)

- □ 1-Mbyte addressable memory

- □ Various memory addressing modes

- □ 14- x 16-bit register set

- □ High-speed block transfers

- $-\mu$ PD70108: 1.0 Mbytes/second (at 8 MHz)

- $-\mu$ PD70116: 2.0 Mbytes/second (at 8 MHz)

- □ Various interrupt processing functions

- □ IEE-796 bus-compatible interface

- ▶ □ 5-, 8-, 10-MHz clock

- 40-pin plastic/ceramic DIP, 44-pin PLCC, and 52-pin plastic miniflat packages

- □ Single +5-volt power source

V20 and V30 are trademarks of NEC Corporation.

#### Figure 1-1. μPD70108/70116 Simplified Block Diagram

#### **Pin Identification**

Table 1 lists pins in alphabetical order by symbol and briefly describes pin functions. Section 2 gives additional descriptions.

Figures 1-2, 1-3, and 1-4 are pin configuration drawings of the four package types: 40-pin plastic or ceramic DIP, 44-pin plastic leaded chip carrier (PLCC), and 52-pin plastic miniflat.

| Symbol                                                             | Direction       | Function (Note 3)                                                            |  |

|--------------------------------------------------------------------|-----------------|------------------------------------------------------------------------------|--|

| A <sub>19</sub> -A <sub>16</sub> /PS <sub>3</sub> -PS <sub>0</sub> | Out             | High-order address bits/<br>Processor status bits                            |  |

| A <sub>15</sub> -A <sub>8</sub> (Note 1)                           | Out             | Middle address bits                                                          |  |

| AD <sub>7</sub> -AD <sub>0</sub> (Note 1)                          | In/Out          | Address/data bus                                                             |  |

| AD <sub>15</sub> -AD <sub>0</sub> (Note 2)                         | In/Out          | Address/data bus                                                             |  |

| ASTB (QS <sub>0</sub> )                                            | Out             | Address strobe<br>(Queue status bit 0)                                       |  |

| BUFEN (BS <sub>0</sub> )                                           | Out             | Buffer enable<br>(Bus status bit 0)                                          |  |

| BUFR/W (BS <sub>1</sub> )                                          | Out             | Buffer read/write<br>(Bus status bit 1)                                      |  |

| CLK                                                                | In              | Clock                                                                        |  |

| GND                                                                |                 | Ground                                                                       |  |

| HLDAK (RQ/AK <sub>1</sub> )                                        | Out<br>(In/Out) | Hold acknowledge output<br>(Bus hold request input/<br>Acknowledge output 1) |  |

| HLDRQ (RQ/AK <sub>0</sub> )                                        | In<br>(In/Out)  | Hold request input<br>(Bus hold request input/<br>Acknowledge output 0)      |  |

| IC                                                                 |                 | Internally connected (Note 4)                                                |  |

| INT                                                                | In              | Maskable interrupt                                                           |  |

| INTAK (QS <sub>1</sub> )                                           | Out             | Interrupt acknowledge<br>(Queue status bit 1)                                |  |

| 10/M (BS <sub>2</sub> )<br>(Note 1)                                | Out             | Access is I/O or memory<br>(Bus status bit 2)                                |  |

| IO/M (BS <sub>2</sub> )<br>(Note 2)                                | Out             | Access is I/O or memory<br>(Bus status bit 2)                                |  |

| LBSO (HIGH)<br>(Note 1)                                            | In              | Latched bus status 0<br>(Always high)                                        |  |

| NC                                                                 |                 | Not connected                                                                |  |

| NMI                                                                | In              | Nonmaskable interrupt                                                        |  |

| POLL                                                               | In              | Poll                                                                         |  |

| RD                                                                 | Out             | Read strobe                                                                  |  |

| READY                                                              | In              | Ready                                                                        |  |

| RESET                                                              | In              | Reset                                                                        |  |

| S/LG                                                               | In              | Small-scale system input/<br>Large-scale system input                        |  |

| UBE (Note 2)                                                       | In              | Upper byte enable                                                            |  |

| V <sub>DD</sub>                                                    |                 | +5-volt power supply                                                         |  |

| WR (BUSLOCK)                                                       | Out             | Write strobe<br>(Bus lock)                                                   |  |

|                                                                    |                 |                                                                              |  |

#### **►** Table 1-1. μPD70108/70116 Pin Identification

Figure 1-2. Pin Configuration, 40-Pin Plastic or Ceramic DIP

| 1                |                 |                                       |

|------------------|-----------------|---------------------------------------|

| IC 🗆             |                 |                                       |

| A <sub>14</sub>  | 2               | 39 🗖 A <sub>15</sub>                  |

| A13 🗆            | 3               | 38 🗖 A <sub>16</sub> /PS <sub>0</sub> |

| A12 🗆            | 4               | 37 🗖 A17/PS1                          |

| A11 🗆            | 5               | 36 🗋 A <sub>18</sub> /PS <sub>2</sub> |

| A10 🗆            | 6               | 35 🗖 A19/PS3                          |

| A9 🗖             | 7               | 34 🗖 LBS0 [HIGH]                      |

| A8 🗖             | 8               | 33 🗖 S/LG                             |

| AD7 🗌            | 9               | 32 🗖 RD                               |

| AD6              | 10 μ <b>Ρ</b> Ε | 31 HLDRQ [RQ/AK0]                     |

| AD5              | 11 7010         | 8 30 🗖 HLDAK [RQ/AK1]                 |

| AD4              | 12              |                                       |

| AD3 🗆            | 13              | 28 🗖 IO/M [BS2]                       |

| AD2              | 14              | 27 🗖 BUFR/W [BS1]                     |

| AD1              | 15              | 26 🗖 BUFEN [BS0]                      |

|                  | 16              | 25 🗖 ASTB [QS0]                       |

| имі 🗆            | 17              | 24 🗖 INTAK [QS1]                      |

|                  | 18              | 23 D POLL                             |

|                  | 19              | 22 🗖 READY                            |

| GND              | 20              | 21 🗖 RESET                            |

|                  |                 |                                       |

|                  |                 |                                       |

| іс 🗆             |                 |                                       |

| AD <sub>14</sub> | 2               | 39 🗖 AD <sub>15</sub>                 |

| AD13             | 3               | 38 🗖 A <sub>16</sub> /PS <sub>0</sub> |

| AD12             | 4               | 37 🗖 A17/PS1                          |

| AD11 🗆           | 5               | 36 🗖 A <sub>18</sub> /PS <sub>2</sub> |

| AD10             | 6               | 35 🗋 A <sub>19</sub> /PS <sub>3</sub> |

| AD9              | 7               | 34 🗖 UBE                              |

| AD8              | 8               | 33 🗖 S/LG                             |

| AD7 🗆            | 9               | 32 🔲 RD                               |

| AD6              | 10 μPC          |                                       |

| AD5 🗆            | 11 7011         | 6 30 🗋 HLDAK [RQ/AK1]                 |

| AD4 🗆            | 12              |                                       |

| AD3 🗆            | 13              | 28 🗖 IO/M [BS2]                       |

| AD <sub>2</sub>  | 14              | 27 🗋 BUFR/W [BS1]                     |

| AD1              | 15              | 26 🛛 BUFEN [BS0]                      |

| $AD_0$           | 16              | 25 🗖 ASTB [QS0]                       |

|                  |                 |                                       |

|                  | 17              | 24 🔲 INTAK [QS1]                      |

|                  | 17<br>18        | 24 🔲 INTAK [QS1]<br>23 🗍 POLL         |

|                  |                 |                                       |

|                  | 18              | 23 DPOLL                              |

|                  | 18<br>19        | 23 ] POLL<br>22 ] READY               |

(4) IC should be connected to ground.

(5). Unused input pins should be tied to ground or  $V_{DD}$  to minimize power dissipation and prevent potentially harmful current flow.

#### Note:

- (1) µPD70108 only.

- (2) µPD70116 only.

- (3) Where pins have different functions in small- and large-scale systems, the large-scale system pin symbol and function are in parentheses.

## Section 1 Introduction

► Figure 1-4. Pin Configuration, 52-Pin Plastic Miniflat

This section describes the functions of input and output signals. Descriptions are in alphabetical order by pin symbol. Unless otherwise specified, they apply to μPD70108 and μPD70116 in small-scale and largescale systems.

The width of the data bus is different for the  $\mu$ PD70108 and  $\mu$ PD70116. Therefore, each microprocessor uses the address/data bus in a different manner.

Memory identification signals for the two processsors are also different. The  $\mu$ PD70108 uses an IO/ $\overline{M}$  signal; the  $\mu$ PD70116 uses an  $\overline{IO}/M$  signal.

## A<sub>19</sub>-A<sub>16</sub>/PS<sub>3</sub>-PS<sub>0</sub> [Address Bus/Processor Status]

These lines are time-multiplexed to operate as an address bus and also to output the processor status signals.

When used as the address bus,  $A_{19}$ - $A_{16}$  are the four high-order bits of the 20-bit memory address. During an I/O bus cycle all four bits are 0.

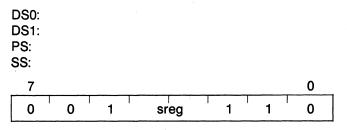

Processor status signals are for memory and I/O use.  $PS_3$  is always 0 in the native mode and always 1 in the emulation mode. The contents of the interrupt enable flag (IE) are carried via  $PS_2$ . Signals  $PS_1$  and  $PS_0$  indicate which memory segment is being accessed.

| A <sub>17</sub> -PS <sub>1</sub> | A <sub>16</sub> -PS <sub>0</sub> | Memory Segment  |

|----------------------------------|----------------------------------|-----------------|

| 0                                | 0                                | Data segment 1  |

| 0                                | 1                                | Stack segment   |

| 1                                | 0                                | Program segment |

| 1                                | 1                                | Data segment 0  |

These pins are tri-state and become high impedance during hold acknowledge.

## A<sub>15</sub>-A<sub>8</sub> [Address Bus]

In the  $\mu$ PD70108 only, A<sub>15</sub>-A<sub>8</sub> are the middle 8 bits of the 20-bit address. This bus is tri-state and becomes high impedance during hold acknowledge. An address bit is 1 when high and 0 when low.

## AD7-AD0 [Address/Data Bus]

In the  $\mu$ PD70108 only, AD<sub>7</sub>-AD<sub>0</sub> is a time-multiplexed address/data bus. These lines output either the lower 8 bits of the 20-bit address or 8 bits of data. Input/output of 16-bit data is performed in two steps: low byte followed by high byte.

This is a tri-state bus and becomes high impedance during hold and interrupt acknowledge. An AD bit is 1 when high and 0 when low.

## AD<sub>15</sub>-AD<sub>0</sub> [Address/Data Bus]

In the  $\mu$ PD70116 only, AD<sub>15</sub>-AD<sub>0</sub> is a time-multiplexed address/data bus. An AD bit is 1 when high and 0 when low. The bus contains the lower 16 bits of the 20-bit address during T1 of the bus cycle. The bus is used as a 16-bit data bus during T2, T3, and T4 of the bus cycle.

The address/data bus is tri-state and can be at a high or low level in standby mode. The bus is at high impedance during hold acknowledge and interrupt acknowledge.

## ASTB [Address Strobe]

In a small-scale system, the CPU generates ASTB to latch address information at an external latch. ASTB is held to a low level in standby mode.

## BS<sub>2</sub>-BS<sub>0</sub> [Bus Status]

In a large-scale system, the CPU uses these status signals to allow an external bus controller to monitor the current bus cycle. The external bus controller decodes  $BS_2$ - $BS_0$  and generates the control signals required to perform a memory or I/O device access.

The  $BS_2$ - $BS_0$  signals are tri-state outputs and become high impedance during hold acknowledge. They are held to a high level in the standby mode.

| BS <sub>2</sub> | BS <sub>1</sub> | BSO | Bus Cycle             |

|-----------------|-----------------|-----|-----------------------|

| 0               | 0               | 0   | Interrupt acknowledge |

| 0               | 0               | 1   | I/O read              |

| 0               | 1               | 0   | I/O write             |

| 0               | 1               | 1   | Halt                  |

| 1               | 0               | 0   | Program fetch         |

| 1               | 0               | 1   | Memory read           |

| 1               | 1               | 0   | Memory write          |

| 1               | 1               | 1   | Passive state         |

## BUFEN [Buffer Enable]

In a small-scale system, BUFEN is used as the output enable signal for an external bidirectional buffer. The CPU generates this signal during data transfer operations with an external memory or I/O device or during the input of an interrupt vector.

The BUFEN signal is held to a high level in the standby mode and becomes high impedance during hold acknowledge.

#### ► BUFR/W [Buffer Read/Write]

In a small-scale system, the level of this signal determines the direction of data transfer with an external bidirectional buffer. A high signal specifies data transmission from the CPU to an external device. A low signal specifies data transmission from the external device to the CPU.

This output can be a high or low level in the standby mode. It becomes high impedance during hold acknowledge.

#### BUSLOCK [Bus Lock]

In a large-scale system, the CPU uses this signal to secure the bus while executing the instruction immediately following the BUSLOCK prefix. The signal inhibits other bus masters in a multiprocessor system from using the system bus during this time. The output is held to a high level in the standby mode, but is a low level if the BUSLOCK instruction is executed immediately before a HALT instruction.

The signal is tri-state and becomes high impedance during hold acknowledge.

#### CLK [Clock]

The CLK pin is the external clock input.

#### HLDAK [Hold Acknowledge]

In a small-scale system, HLDAK indicates the CPU has accepted a hold request signal (HLDRQ). While HLDAK is high, the address bus, address/data bus, and control lines are held in the high-impedance state.

#### HLDRQ [Hold Request]

In a small-scale system, external devices input the HLDRQ signal to request that the CPU release the address, address/data, and control buses.

#### IC [Internally Connected]

The IC pin is used for factory tests. Normally, the  $\mu$ PD70108/70116 is used with this pin at ground potential.

#### INT [Maskable Interrupt]

The INT pin is used for interrupt requests that can be masked by software. This input is an active high level and is sensed during the last clock of the current instruction. The interrupt will be accepted if the system is in the interrupt enable state (interrupt enable flag IE = 1). The CPU generates INTAK to notify external devices that the interrupt request is being acknowledged. INT must be held high until the INTAK signal is returned.

If NMI and INT interrupts occur at the same time, NMI has priority and INT will not be accepted. A hold request will be accepted even during interrupt acknowledge.

INT causes the microprocessor to exit the standby mode.

#### **INTAK** [Interrupt Acknowledge]

In a small-scale system, when the CPU accepts an INT signal, it asserts the INTAK signal active low. The interrupting device synchronizes with the signal and puts the interrupt vector number on the data bus  $(AD_7-AD_0)$ .

During standby mode, INTAK is held to a high level.

#### IO/M [IO/Memory]

In a small-scale  $\mu$ PD70108 system, the CPU outputs this signal to indicate either an I/O or memory access. A high-level output specifies an I/O access and a lowlevel output specifies a memory access. This output can be a high or low level in the standby mode.

The pin is tri-state and becomes high impedance during hold acknowledge.

## IO/M [IO/Memory]

In a small-scale  $\mu$ PD70116 system, the CPU generates this signal to specify either an I/O access or a memory access. A low-level output specifies an I/O access and a high-level output specifies a memory access. The output can be a high or low level in the standby mode.

The pin is tri-state and becomes high impedance during hold acknowledge.

#### LBS0 [Latched Bus Status 0]

In a small-scale  $\mu$ PD70108 system, the CPU uses this signal (along with the IO/ $\overline{M}$  and BUFR/W signals) to inform external devices of the status of the current bus cycle. See below.

| 10/M | BUFR/W | LBSO | BUS Cycle             |

|------|--------|------|-----------------------|

| 0    | 0      | 0    | Program fetch         |

| 0    | 0      | 1    | Memory read           |

| 0    | 1      | 0    | Memory write          |

| 0    | 1      | 1    | Passive state         |

| 1    | 0      | 0    | Interrupt acknowledge |

| 1    | 0      | 1    | I/O read              |

| 1    | 1      | 0    | I/O write             |

| 1    | 1      | 1    | Held                  |

|      |        |      |                       |

#### NMI [Nonmaskable Interrupt]

The NMI signal is used for interrupt requests that cannot be masked by software The interrupt is triggered on the rising edge of NMI and can be sensed during any clock cycle. NMI must be held high for at least five clock cycles after its rising edge. Actual interrupt processing begins after completion of the instruction in progress.

The contents of interrupt vector 2 determines the starting address for the interrupt servicing routine. A hold request will be accepted even during NMI acknowledge. This interrupt will cause the micro-processor to exit the standby mode.

#### POLL [Poll]

The CPU checks the input at this pin when executing the POLL instruction. If the input is low, execution continues. If the input is high, the CPU will check the state of the input every five clock cycles until the input again becomes low.

These functions synchronize CPU program execution with the operation of external devices.

#### QS<sub>1</sub>, QS<sub>0</sub> [Queue Status]

In a large-scale system, the CPU uses  $QS_1$  and  $QS_0$  to allow external devices, such as the floating-point arithmetic processor chip, to monitor the status of the internal CPU instruction queue.

| QS <sub>1</sub> | QSO | Instruction Queue Status                        |

|-----------------|-----|-------------------------------------------------|

| 0               | 0   | NOP (queue did not change)                      |

| 0               | 1   | First byte of an instruction taken from queue   |

| 1               | 0   | Flush queue                                     |

| 1               | 1   | Subsequent byte of instruction taken from queue |

The instruction queue status indicated by these signals is the status when the execution unit (EXU) accesses the instruction queue. The data output from  $QS_0$  and  $QS_1$  is therefore valid only for one clock immediately following queue access.

$QS_1$  and  $QS_0$  enable the floating-point processor chip to monitor the CPU's program execution status. In this manner, the floating-point processor can synchronize its operation with the CPU whenever it gains control from a floating-point operation instruction (FPO).

$QS_1$  and  $QS_0$  are held to a low level during standby mode.

## **RD** [Read Strobe]

The CPU outputs the  $\overline{RD}$  signal during a data read from an I/O device or memory. The IO/M or  $\overline{IO}/M$  signal determines whether the read is I/O or memory.  $\overline{RD}$  is a tri-state output and becomes high impedance during a hold acknowledge.

#### **READY** [Ready]

READY indicates that the data transfer is complete. A high indicates READY is true; a low indicates READY is false (not ready).

When READY goes high during a read cycle, the data is latched one clock cycle later and the bus cycle is terminated. When READY goes high during a write cycle, the bus cycle is terminated one clock cycle later.

#### RESET [Reset]

RESET is the CPU reset signal and is an active high level. This signal has priority over all other operations. After RESET returns to the low level, the CPU begins execution of the program starting at address FFFF0H.

RESET causes the microprocessor to exit the standby mode.

## **RQ/AK1, RQ/AK0** Hold Request Acknowledge

In a large-scale system, these pins function as the bus hold request inputs ( $\overline{RQ}$ ), and the bus hold acknow-ledge outputs ( $\overline{AK}$ ). The  $\overline{RQ}/\overline{AK_0}$  signal has priority over the  $\overline{RQ}/\overline{AK_1}$  signal.

These signals have tri-state outputs with on-chip pullup resistors that keep the pins at a high level when the output is at the high-impedance state.

## S/LG [Small/Large]

This signal determines the operating mode of the CPU. The signal is fixed at either a high or low level. When the signal is high level, the CPU operates in the smallscale system mode. When the signal is low level, the CPU operates in the large-scale system mode. A smallscale system will have at most one additional bus master requesting use of the bus. A large-scale system can have more than one.

As noted in table 1-1, some pins have different symbols and functions in small-scale and large-scale systems.

## UBE [Upper Byte Enable]

UBE indicates the use of the upper 8 bits  $(AD_{15}-AD_8)$  of the data bus. This signal is active low during T1-T4 of the bus cycle. Bus cycles in which the signal is active are shown below:

| Type of<br>Bus Operation | UBE       | AD <sub>o</sub> | Number of<br>Bus Cycles |

|--------------------------|-----------|-----------------|-------------------------|

| Word to even address     | 0         | 0               | . 1                     |

| Word to odd address      | 0*<br>1** | 1<br>0          | 2                       |

| Byte to even address     | 1         | 0               | 1                       |

| Byte to odd address      | 0         | 1               | 1                       |

\* First bus cycle

\*\* Second bus cycle

UBE goes low continuously during the interrupt acknowledge state. The signal is held high during standby mode. The signal is a tri-state output and becomes high impedance during a hold acknowledge.

Section 4, Memory Accessing, contains detailed information on the use of UBE.

## WR [Write Strobe]

In a small-scale system, the CPU asserts  $\overline{\text{WR}}$  during a write to an I/O device or memory. The IO/M or IO/M signal selects either I/O or memory. The  $\overline{\text{WR}}$  output is held to a high level in the standby mode.

The pin is tri-state and becomes high impedance during hold acknowledge.

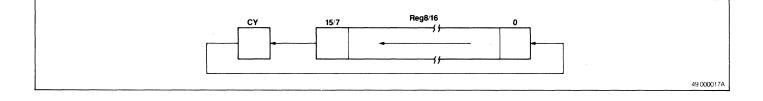

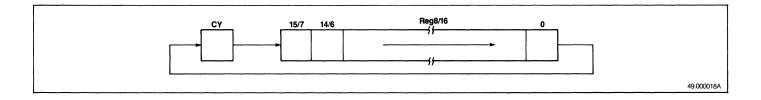

As shown in figure 3-1, the  $\mu$ PD70108 and  $\mu$ PD70116 both contain two internal, independent processing units: an execution unit (EXU) and a bus control unit (BCU).

The EXU controls the internal data processing that executes the instruction set of the  $\mu$ PD70108/70116.

The BCU is the interface between the EXU and the external bus. It prefetches instructions for the instruction queue — 4 bytes in the  $\mu$ PD70108 and 6 bytes in the  $\mu$ PD70116. It also accesses memory (upon request from the EXU) for additional operands, or stores EXU results.

## **EXECUTION UNIT (EXU)**

The EXU includes the following functional elements:

- Program Counter

- General Purpose Registers (AW, BW, CW, DW)

- Pointers (SP, BP) and Index Registers (IX, IY)

- Temporary Register/Shifter (TA/TB)

- Temporary Register C (TC)

- Arithmetic and Logic Unit (ALU)

- Program Status Word (PSW)

- Loop Counter (LC)

- Effective Address Generator (EAG)

- Instruction Decoder

- Microaddress Register

- Microinstruction ROM

- Microinstruction Sequencer

- Dual data bus

## Program Counter (PC)

The program counter is a 16-bit binary counter that contains the segment offset of the program memory address of the next instruction which the EXU is to execute.

The PC increments each time the microprogram fetches a byte from the instruction queue. A new location value is loaded into the PC each time a branch, call, return, or break instruction is executed. At this time, the contents of the PC are the same as the Prefetch Pointer (PFP).

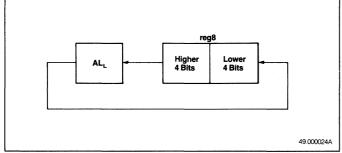

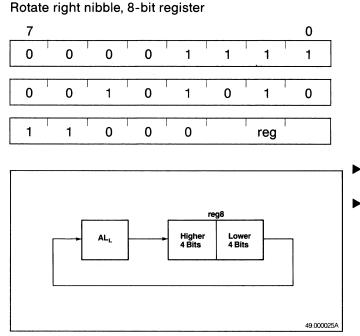

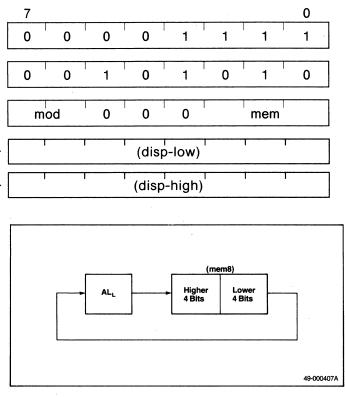

#### General Purpose Registers (AW, BW, CW, DW)

There are four 16-bit general-purpose registers. Each one can be used as one 16-bit register or as two 8-bit registers. This is accomplished by dividing the registers into their high and low bytes (AH, AL, BH, BL, CH, CL, DH, DL).

Each register is also used as a default register for processing specific instructions. The default assignments are:

- AW Word multiplication/division, word I/O, data conversion

- AL Byte multiplication/division, byte I/O, BCD rotation, data conversion, translation

- AH Byte multiplication/division

- BW Translation

- CW Loop control branch, repeat prefix

- CL Shift instructions, rotation instructions, BCD operations

- DW Word multiplication/division, indirect addressing, I/O

#### Pointers (SP, BP) and Index Registers (IX, IY)

These registers serve as base pointers or index registers when accessing memory using based, indexed, or base indexed addressing.

These registers can also be used for data transfer and arithmetic and logical operations in the same manner as the general-purpose registers. They cannot be used in these areas as 8-bit registers.

Also, the SP, IX, and IY registers act as default registers for specific operations. The default assignments are:

- SP Stack operations

- IX Block transfer, BCD string operations (source)

- IY Block transfer, BCD string operations (destination)

#### Temporary Register/Shifter (TA/TB)

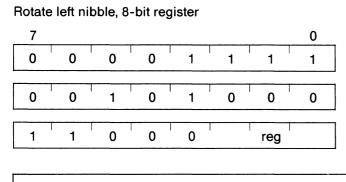

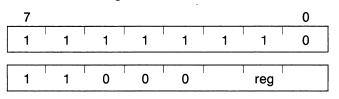

TA/TB are 16-bit temporary registers/shifters used in the execution of multiply/divide and shift/rotate (including BCD rotate) instructions. Execution of multiplication/division instructions can be accomplished approximately four times faster than when using the microprogramming method.

When executing a multiply or divide instruction, TA+TB operates as a 32-bit temporary register/shifter. TB operates as a 16-bit temporary register/shifter when executing shift/rotate instructions. Both TA and TB can be read from or written to. When this is done from the internal bus, the upper byte and lower byte may be accessed independently. The contents of TA and TB are inputs to the ALU.

#### **Temporary Register C (TC)**

The TC is a 16-bit temporary register used for internal processing such as a multiply or divide operation. The contents of TC are inputs to the ALU.

#### Arithmetic and Logic Unit (ALU)

The ALU consists of a full adder and a logical operation unit. The ALU performs the following arithmetic operations:

## $\mu$ PD70108/70116

Figure 3-4. µPD70108/70116 Block Diagram

# NEC

- Add, subtract, multiply, and divide

- Increment, decrement, and two's complement

The ALU also performs the following logical operations:

- AND, OR, XOR, complement

- Bit test, set, clear, and complement

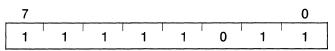

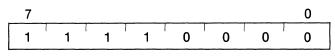

#### **Program Status Word (PSW)**

The PSW contains six status flags:

- V (Overflow)

- S (Sign)

- Z (Zero)

- AC (Auxiliary carry)

- P (Parity)

- CY (Carry)

The program status word also contains four control flags:

- MD (Mode)

- DIR (Direction)

- IE (Interrupt enable)

- BRK (Break)

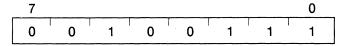

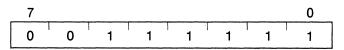

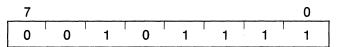

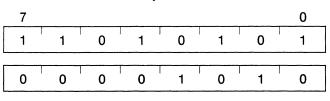

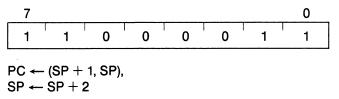

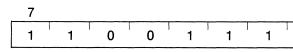

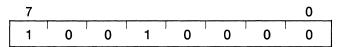

When the PSW is pushed onto the stack, the word format of the various flags is as follows:

#### PSW

| 15     | 14 | 13 | 12 | 11 | 10          | 9      | 8 | 7 | 6 | 5 | 4      | 3 | 2 | 1 | 0      |

|--------|----|----|----|----|-------------|--------|---|---|---|---|--------|---|---|---|--------|

| M<br>D | 1  | 1  | 1  | ۷  | D<br>I<br>R | I<br>E |   | S | Z | 0 | A<br>C | 0 | Ρ | 1 | C<br>Y |

The status flags are set and reset depending on the result of each type of instruction executed. Instructions are provided that set, reset, and complement the CY flag directly. Other instructions set and reset the control flags and control the operation of the CPU.

## Loop Counter (LC)

The loop counter (LC) is a 16-bit register which counts:

- Loop times specified in the primitive block transfer

- I/O instructions controlled with repeat prefix instructions such as REP and REPC

- Shifts for the multi-bit shift/rotate instructions

The processing speed for multiple-bit rotation of a register is approximately twice as fast as when using the microprogram method.

Example:

RORC AW, CL ; CL = 5

Microprogram Method Loop Cou

$8 + (4 \times 5) = 28$  clocks

Loop Counter Method

7+5=12 clocks

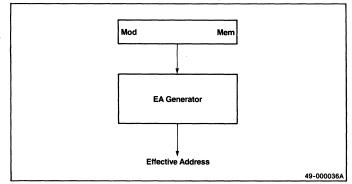

#### **Effective Address Generator (EAG)**

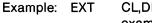

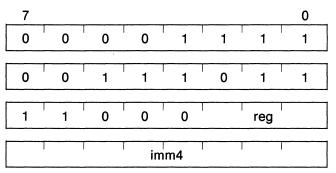

The effective address generator (EAG) performs a highspeed effective address calculation for memory access. While the microprogramming method normally requires 5 to 12 clock cycles to calculate an address, the EAG completes all the EA calculations in 2 clocks for all addressing modes (see figure 3-2).

The EXU fetches the instruction bytes that have the operand field and determines if the instruction will require a memory access. If it does, the EAG calculates the effective address and transfers it to the DP (data pointer) which generates control signals that handle the ALU and corresponding registers. In addition, if it is necessary, the EAG requests a bus cycle from the BCU.

#### Instruction Decoder

The instruction decoder decodes the first byte of an instruction into groups with specific functions and holds them during the instruction execution.

#### **Microaddress Register**

The microaddress register specifies the starting address in the microinstruction ROM of the next instruction to be executed. At the beginning of a new instruction, the first byte of the instruction is taken from the prefetch queue and put into the microaddress register. The register then specifies the starting address of the corresponding microinstruction sequence.

#### **Microinstruction ROM**

The microinstruction ROM has 1024 microinstructions. Each microinstruction is 29 bits wide.

Figure 3-2. Effective Address Generator

#### **Microinstruction Sequencer**

The microinstruction sequencer controls the microaddress register operation, microinstruction ROM output, and the synchronization of the EXU with the BCU.

#### **Dual Data Bus**

The  $\mu$ PD70108/70116 contains a dual, 16-bit data bus that consists of a main and subdata bus. The dual data bus reduces the number of processing steps for instruction execution. For addition/subtraction and logical and comparison operations, processing time is approximately 30% faster then in single-bus systems.

Example:

ADD AW, BW :AW ← AW + BW **Single-Bus System Dual-Bus System** 1. TA ← AW TA ← AW, TB ← BW 2. TB ← BW

3. AW ← TA + TB

## AW $\leftarrow$ TA + TB

## **BUS CONTROL UNIT (BCU)**

The BCU includes the following functional elements:

- Prefetch Pointer (PFP)

- Prefetch Queue (Q<sub>0</sub>-Q<sub>3</sub>/Q<sub>0</sub>-Q<sub>5</sub>)

- Data Pointer (DP)

- Temporary Communication Register (TEMP)

- Segment Registers (PS, SS, DS<sub>0</sub>, DS<sub>1</sub>)

- Address Modifier (ADM)

#### **Prefetch Pointer (PFP)**

The PFP is a 16-bit binary counter that contains a program segment offset. The offset is used to calculate a physical address that the Bus Control Unit (BCU) uses to prefetch the next byte or word for the instruction queue. The contents of the PFP are an offset from the Program Segment register (PS).

The PFP is incremented each time the BCU prefetches an instruction from the program memory. A new location will be loaded into the PFP whenever a branch, call, return, or break instruction is executed - this provides a time savings of several clocks since the PC does not require adjustment. At that time, the contents of the PFP will be the same as those of the program counter (PC).

## Prefetch Queue (Q<sub>0</sub>-Q<sub>3</sub>/Q<sub>0</sub>-Q<sub>5</sub>)

The  $\mu$ PD70108/70116 has a prefetch queue that can store 4/6 instruction bytes that are prefetched by the BCU. The instruction bytes stored in the queue are taken from the queue and executed by the EXU. The queue is cleared when a branch, call, return, or break instruction has been executed, or when an external interrupt has been acknowledged.

Normally, the  $\mu$ PD70108 prefetches a byte if the queue has one or more empty bytes. The  $\mu$ PD70116 prefetches if the queue has one or more empty words (two bytes). If the time required to prefetch the instruction code from external memory is less than the mean execution time of instructions executed sequentially, the actual instruction cycle will be shortened by the time needed to fetch the instructions. This occurs because the next instruction code to be executed by the EXU will be available in the queue immediately after the completion of the previous instruction. As a result, the processing speed is increased when compared with a conventional CPU where the fetch and execute times do not overlap.

The queuing effect will be lowered if there are many instructions which clear the queue; for example, a branch instruction, or a series of instructions with a short instruction time.

## Data Pointer (DP)

The DP is a 16-bit register that contains the read/write addresses of variables. Effective addresses calculated by the effective address generator are transferred to the DP.

#### **Temporary Communication Register (TEMP)**

The TEMP is a 16-bit temporary register that stores data being transferred between the external data bus and the EXU.

The TEMP can be read from or written to independently by the upper or lower byte. Basically, the EXU completes a write operation by transferring data to the TEMP and completes a read operation by taking the data transferred to the TEMP from the external data bus.

#### Segment Registers (PS, SS, DS<sub>0</sub>, DS<sub>1</sub>)

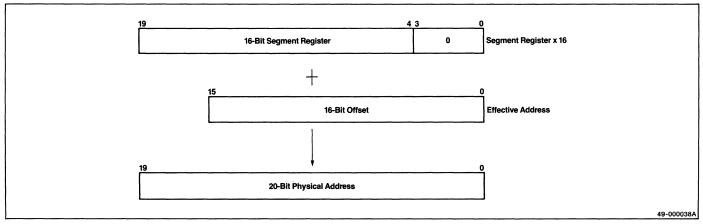

The memory addresses accessed by the  $\mu$ PD70108/ 70116 are divided into 64 Kbyte logical segments. The starting (base) address of each segment is specified by a segment register. The offset from this starting address is specified by the contents of another register or by the effective address.

The  $\mu$ PD70108/70116 uses four types of segment registers:

| Segment Register                 | Default Offset        |

|----------------------------------|-----------------------|

| PS (Program Segment)             | PFP                   |

| SS (Stack Segment)               | SP, Effective Address |

| DS <sub>0</sub> (Data Segment 0) | IX, Effective Address |

| DS <sub>1</sub> (Data Segment 1) | IY, Effective Address |

#### **Address Modifier (ADM)**

The address modifier logic generates a physical memory or I/O address by adding the segment register and PFP (or DP) contents.

## **MEMORY CONFIGURATION**

Memory contains instructions, interrupt handler start addresses, stack data, and general data. Some of this data is stored in bytes and other in words. The  $\mu$ PD70108/70116 can access up to 1 Mbyte (512 Kwords) of memory by using the 20-bit address bus (A<sub>19</sub>-A<sub>0</sub>).

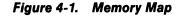

As the memory map in figure 4-1 shows, the first 1 Kbytes of addresses (0H-3FFH) are used for the interrupt vector table. Parts of this area may also be used for other purposes in some systems. The 12 bytes from address FFFF0H to FFFFBH are always used by the CPU when it is reset, and therefore cannot be used for any other purpose.

The four bytes from addresses FFFFCH to FFFFFH are reserved for future use and are not available.

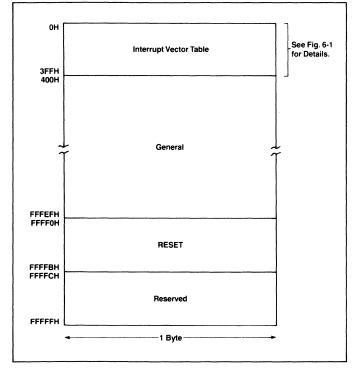

Memory data can be stored in both even  $(A_0 = 0)$  and odd  $(A_0 = 1)$  addresses. The area where the interrupt start addresses (interrupt vector table) are stored must use even addresses. The  $\mu$ PD70116 can access a word regardless of whether the word is at an even or odd address. This allows both even and odd addresses to be used for an instruction. Table 4-1 shows the type and configuration of data, and address requirements. Figure 4-2 shows the placement of word and double word data in memory.

| Table 4-1 | Data | Type | and | Addres | ssing    |

|-----------|------|------|-----|--------|----------|

| Nete      |      |      | Add | -      | Date Con |

| Data                   | Address     | Data Configuration1-6 bytes2 words/vector |  |

|------------------------|-------------|-------------------------------------------|--|

| Instruction Code       | Even or odd |                                           |  |

| Interrupt Vector Table | Even        |                                           |  |

| Stack                  | Even or odd | Word                                      |  |

| General Variable       | Even or odd | Byte, word, or double word                |  |

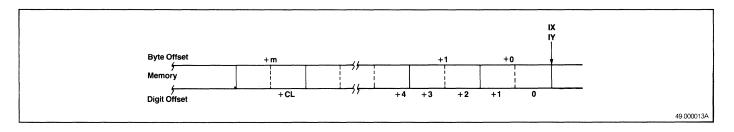

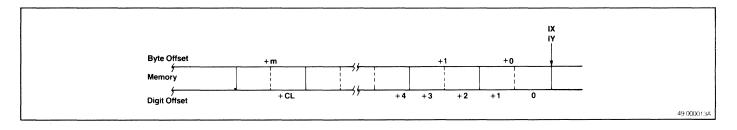

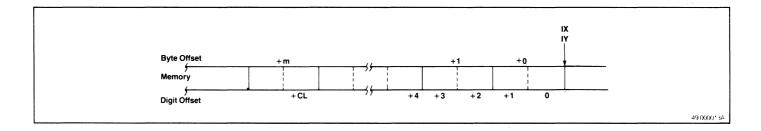

#### Figure 4-2. Word and Double Word Placement in Memory

## **MEMORY ACCESSING**

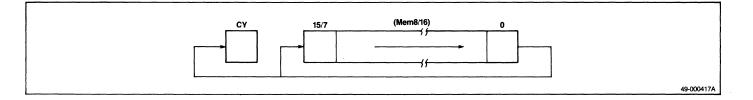

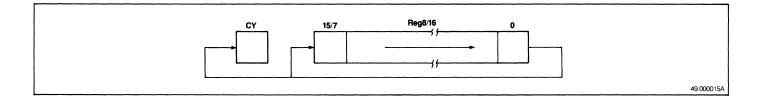

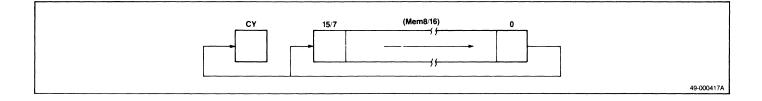

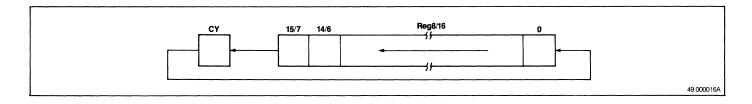

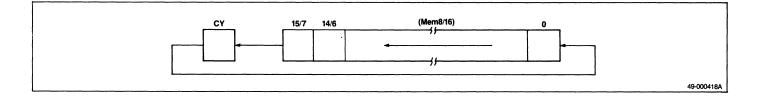

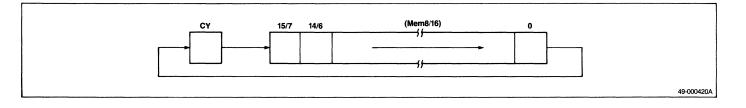

Since the  $\mu$ PD70108 data bus is only 8 bits wide, only one byte (8 bits) is accessed during one bus cycle. Two bus cycles are required to access a data word from either an even or odd address. Figure 4-3 shows the interface between memory and the  $\mu$ PD70108. Figure 4-4 shows the interface between memory and the  $\mu$ PD70116.

The address space for the  $\mu$ PD70116 is 1 Mbyte, but because the  $\mu$ PD70116 can transfer both bytes and words of data, the physical memory appears to be two banks, each containing 512 Kbytes of data (figure 4-4). Data lines  $D_7$ - $D_0$  are connected to the low-order memory bank and address bit  $A_0$  selects this bank when  $A_0=0$ . Data lines  $D_{15}$ - $D_8$  are connected to the high-order memory bank and signal UBE is used to select this bank when UBE is low. Address bits 19-1 contain the physical address within a data bank where the byte of data is to be accessed.

Figure 4-4. µPD70116 Memory Interface

The following chart shows how  $A_0$  and  $\overline{UBE}$  are used. Memory transfer operations are described after the chart.

| Type of Bus<br>Operation | UBE       | Ao     | Number of Bus Cycles |

|--------------------------|-----------|--------|----------------------|

| Word to even address     | 0         | 0      | 1                    |

| Word to odd address      | 0*<br>1** | 1<br>0 | 2                    |

| Byte to even address     | 1         | 0      | 1                    |

| Byte to odd address      | 0         | 1      | 1                    |

Notes: \* First bus cycle

\*\* Second bus cycle

When transferring a word of data to an even address, the  $\mu$ PD70116 puts the low-order data byte on D<sub>7</sub>-D<sub>0</sub>, the high-order data byte on D<sub>15</sub>-D<sub>8</sub>, and sets both UBE and A<sub>0</sub> to 0. In this manner, both the low- and high-order memory banks are simultaneously selected and the transfer is performed in one bus cycle.

The transfer of a word of data to an odd address requires two bus cycles. In the first cycle, the  $\mu$ PD70116 puts the low-order data byte on D<sub>15</sub>-D<sub>8</sub>, sets UBE to 0, sets A<sub>0</sub> to one, and transfers the first byte to the high-order memory bank. In the second cycle, the  $\mu$ PD70116 increments the address by +1, puts the high-order data byte on D<sub>7</sub>-D<sub>0</sub>, sets UBE to 1, sets A<sub>0</sub> to 0, and transfers the second byte to the low-order data bank.

When transferring a byte of data to an even address, the  $\mu$ PD70116 puts the data byte on D<sub>7</sub>-D<sub>0</sub>, sets UBE to 1, A<sub>0</sub> to 0, and transfers the data byte to the low-order memory bank.

When transferring a byte of data to an odd address, the  $\mu$ PD70116 puts the data byte on D<sub>15</sub>-D<sub>8</sub>, sets UBE to 0, sets A<sub>0</sub> to 1, and transfers the data byte to the high-order memory bank.

The  $\mu$ PD70116 normally prefetches instruction codes in words. However, if a branch operation to an odd address takes place, only one byte is fetched from that odd address. After that, instruction codes are prefetched in words.

When the interrupt vector table is accessed in response to an interrupt, even addresses are always used. During an interrupt, two bus cycles are required because two words (segment base, and offset) are required.

One memory bus cycle requires four clocks. Thus, each time a word from an odd address is accessed, four additional clocks are required than when accessing an evenaddress word. When transferring a word from one memory area to another, the memory must be accessed twice. The word must be read from the source first and then written to the destination. If both the source and the destination are odd addresses, the execution time will be maximized. The following example shows the number of clocks required to execute the MOV reg, mem instruction for both a byte and word of data.

| Data  | Processor                       | Number of Clocks |  |

|-------|---------------------------------|------------------|--|

| Bytes | µPD70108/70116                  | 11               |  |

| Words | µPD70116 (even address)         | 11               |  |

| Words | μPD70108/70116 (odd<br>address) | 15               |  |

The above stack information is also true during a stack operation since all stack data is organized as words. Twice as many bus cycles are required during a stack operation using an odd rather than even address.

## **I/O CONFIGURATION AND ACCESSING**

The  $\mu$ PD70108/70116 can access up to 64 Kbytes (32 Kwords) of I/O address area independent of memory. However, the upper 256 bytes (FF00H-FFFFH) are reserved by NEC for future use. The I/O address area is addressed by the lower 16 bits of the address bus. Figure 4-5 shows the I/O map.

Unlike memory, segment registers are not used in I/O. When the address bus carries I/O addresses, address bits  $A_{19}$ - $A_{16}$  are all zeros. Since data is transferred between the CPU and I/O in bytes or words, both 8-bit and 16-bit I/O devices can be connected to the  $\mu$ PD70116. Only 8-bit I/O devices can be connected to the  $\mu$ PD70108.

In the  $\mu$ PD70116, only one bus cycle is required to access a word on an even address; two bus cycles are required to access a word on an odd address.

When the  $\mu$ PD70116 accesses an 8-bit I/O device, bits A<sub>0</sub> and UBE select the device. Bit A<sub>1</sub> and higher bits select a device and the registers within that device. When

##

Figure 4-5. I/O Map

accessing 8-bit I/O devices, only even addresses should be assigned to the device and its internal registers. This allows the registers to be selected using only even addresses. Similarly, 8-bit I/O devices with internal registers assigned odd addresses must be accessed using odd addresses.

If a memory-mapped I/O configuration (memory address space allocated to an I/O device) is used, the I/O addresses can be allocated to a portion of the 1 Mbyte memory area. In this manner, all CPU addressing modes and instructions can be directly performed on the I/O device. For example, if a bit operation instruction for memory is used, one line of a specific I/O port can be tested for 1 or 0, set to 1, cleared to 0, or inverted. In a memory-mapped I/O configuration, control signals from the CPU are used exactly as for memory. Therefore, the I/O device is distinguished from memory only by its address. Care must be taken so that addresses of variables or the stack do not conflict with the addresses allocated to a memory-mapped I/O device.

#### **Bus Cycles and Memory Access**

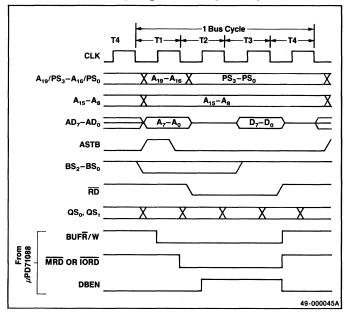

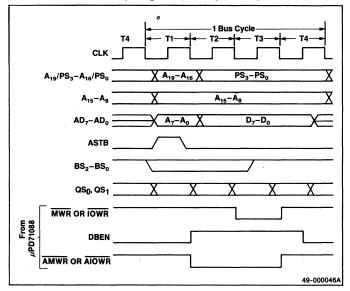

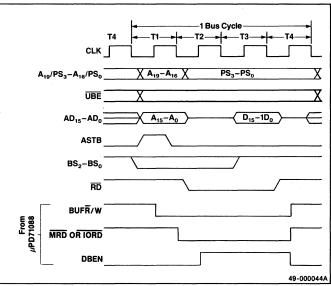

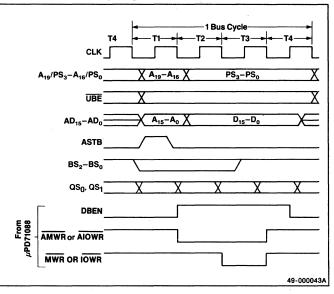

One bus cycle is required for each access (read/write) of memory or I/O. A bus cycle is basically made up of four states (clocks): T1 through T4. When the microprocessor operates at 8 MHz, one state is 125 ns. The  $\mu$ PD70108 and  $\mu$ PD70116 fetch instructions and read data, using exactly the same timing (figures 5-1, 5-3, 5-5, and 5-7).

Figure 5-2. Write Timing of µPD70108 Memory and I/O (Small-Scale Systems)

The EXU fetches an instruction from the instruction queue and executes it. The BCU continues prefetching instructions for the instruction queue until the queue becomes full. If the EXU does not fetch an instruction from the queue because another instruction is still being executed and the instruction queue is full, the BCU will not prefetch the next instruction. Instead, it automatically inserts an idle state (TI) after state T3. More idle states

Figure 5-3. Read Timing of  $\mu$ PD70116 Memory and I/O (Small-Scale Systems)

Figure 5-4. Write Timing of  $\mu$ PD70116 Memory and I/O (Small-Scale Systems)

are inserted until the EXU finishes executing the instruction being processed. Then it fetches the next instruction from the instruction queue. When the next instruction is fetched, the BCU advances the state of the bus cycle from state T4 to T1.

When a memory or I/O device has a long access time, the BCU samples the READY signal (sent from memory or an I/O device). If READY is low, the BCU will insert wait states TW between T3 and T4. When READY

## Figure 5-5. Read Timing of µPD70108 Memory and I/O (Large-Scale Systems)

Figure 5-6. Write Timing of µPD70108 Memory and I/O (Large-Scale Systems)

becomes high, the BCU goes to T4 and then to T1 so that the next instruction can be fetched. When wait state TW is inserted, the current level of each signal is not changed and the read/write timing is longer for that cycle.

Figures 5-1 through 5-8 show read/write timing for  $\mu$ PD70108/70116 memory and I/O. The timing diagrams are for small- and large-scale systems.

## Figure 5-7. Read Timing of µPD70116 Memory and I/O (Large-Scale Systems)

Figure 5-8. Write Timing of µPD70116 Memory and I/O (Large-Scale Systems)

There are two types of interrupts in the  $\mu$ PD70108/70116. One is caused by an external interrupt request and the other is caused internally by software. Both types of inter-

rupts are vectored. When an interrupt occurs, a location in the interrupt vector table is selected either automatically (fixed vector) or by software (variable vector). This selected location determines the start address of the corresponding interrupt routine.

Table 6-1 shows the types of interrupts, interrupt source, number of clocks required to process each interrupt, vector, and priority.

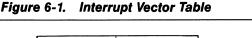

Figure 6-1 shows the interrupt vector table. This table is allocated in a 1 Kbyte memory area (addresses 000H to 3FFH) and can hold up to 256 vectors (four bytes required per vector).

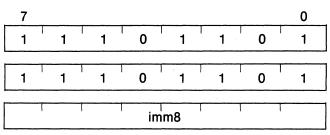

The interrupt sources for vectors 0 to 5 are predetermined and vectors 6 to 31 are reserved for future use. Vectors 32 to 255 are for general use. These vectors are used for the four interrupt sources: 2-byte break, BRKEM, CALLN instructions (during emulation), and INT input.

Four bytes are used for each interrupt vector. The two bytes of the lower address and the two bytes of the higher address are loaded respectively into the program counter (PC) as an offset, and a segment register (PS) as a base.

|          | Interrupt Source               | No. of<br>Clocks* | Vector | Priority |  |

|----------|--------------------------------|-------------------|--------|----------|--|

| External | NMI (rising-edge<br>triggered) | 58/38             | 2      | 2        |  |

|          | INT (high-level active)        | 68/49             | 32-255 | 3        |  |

| Software | DIVU divide by 0 error         | 65/45             |        |          |  |

|          | DIV divide by 0 error          | 65-75/<br>45-55   | 0      |          |  |

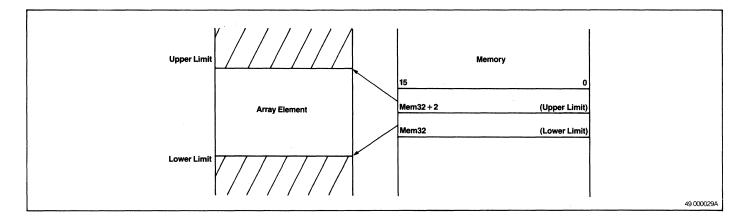

|          | CHKIND boundary<br>over        | 81-84/<br>53-56   | 5      | 1        |  |

|          | BRKV instruction               | 60/40             | 4      | -        |  |

|          | BRK3 (breakpoint)              |                   | 3      | -        |  |

|          | BRK imm8                       | 58/38             |        | -        |  |

|          | BRKEM imm8<br>CALLN imm8       |                   | 32-255 |          |  |

|          | BRK flag<br>(single step)      |                   | 1      | 4        |  |

Note: \*The number to the left of the slash (/) is for the  $\mu$ PD70108 and the number to the right is for the  $\mu$ PD70116.

Example: Vector 0

| Location | 0H |          |        | 00H                          |

|----------|----|----------|--------|------------------------------|

|          | 1H |          |        | 01H                          |

|          | 2H |          |        | 02H                          |

|          | 3H | 03H      |        |                              |

|          |    | PS<br>PC | ↓<br>↓ | (003H, 002H)<br>(001H, 000H) |

The contents of the vectors are initialized at the beginning of a program. The basic steps when program execution jumps to an interrupt routine are:

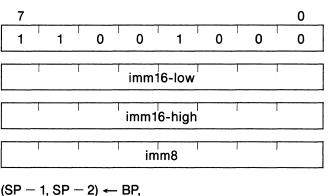

| (SP-1, SP-2) ← PSW                             |

|------------------------------------------------|

| (SP-3, SP-4) ← PS                              |

| (SP-5, SP-6) ← PC                              |

| SP ← SP-6                                      |

| IE ← 0, BRK ← 0, MD ← 1                        |

| PS ← higher vector from interrupt vector table |

| PC ← lower vector from interrupt vector table  |

The interrupt enable (IE) and break (BRK) flags are reset when an interrupt routine is started. Therefore, maskable interrupts (INT) and single-step interrupts are disabled.

## **MASKABLE INTERRUPTS**

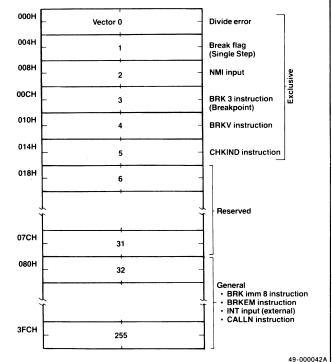

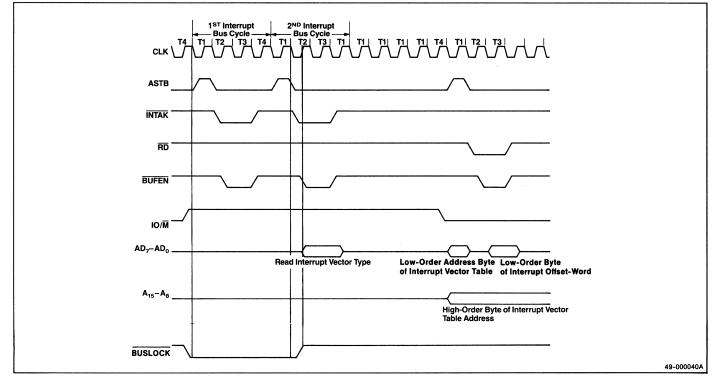

If an INT input signal is a high level at the end of an instruction and the interrupt is enabled (IE = 1), the INT interrupt request will be acknowledged, unless the NMI or hold request signals are active at the same time. The program execution then enters an interrupt acknowledge cycle (figures 6-2 and 6-3).

The interrupt acknowledge cycle consists of two bus cycles. The INTAK, ASTB, and BUFEN signals are generated during the first cycle. Although the bus cycle is started, no read/write operation is performed and the address/data bus becomes high impedance. During this time, a hold request is not accepted. If the  $\mu$ PD70108/70116 is in the maximum mode, the BUS-

LOCK signal is also generated inhibiting other devices from using the bus. Figures 6-2 and 6-3 show the timing for the interrupt acknowledge bus cycles.

The first interrupt acknowledge cycle is necessary to synchronize the external interrupt controller with the  $\mu$ PD70108/70116. When the INTAK, ASTB, and BUFEN signals are output during the second interrupt acknowledge cycle, the external interrupt controller puts the interrupt vector number on the data bus (AD<sub>7</sub>-AD<sub>0</sub>).

After the second interrupt acknowledge cycle has been completed, the location in the interrupt vector table corresponding to the vector obtained during the interrupt acknowledge cycle is accessed. Before calling the interrupt routine, the contents of the PSW, PS, and PC are saved in the stack. The interrupt start address is then loaded into the PS and PC registers from the interrupt vector table and the interrupt routine is started.

The following are sequential lists of interrupt acknowledge operations performed by the  $\mu$ PD70108 and  $\mu$ PD70116.

#### μ**PD70108**

- (1) Acknowledge cycle (first)

- (2) Acknowledge cycle (second)

- (3) Save lower byte of PSW to stack

- (4) Save higher byte of PSW to stack

- (5) Save lower byte of PS to stack

- (6) Save higher byte of PS to stack

- (7) Save lower byte of PC to stack

- (8) Save higher byte of PC to stack

- (9) SP  $\leftarrow$  SP-6

- (10) Read lower byte of offset word to PC

- (11) Read higher byte of offset word to PC

- (12) Read lower byte of segment word to PS

- (13) Read higher byte of segment word to PS

- (14) Jump to interrupt start address

#### μ**PD70116**

- (1) Acknowledge cycle (first)

- (2) Acknowledge cycle (second)

- (3) Save PSW word to stack

- (4) Save PS word to stack

- (5) Save PC word to stack

- (6) SP ← SP-6

- (7) Read offset word to PC

- (8) Read segment word to PS

- (9) Jump to interrupt start address

During the first  $\mu$ PD70108 interrupt acknowledge bus cycle, no idle TI states are inserted in the bus cycle. However, the  $\mu$ PD70116 inserts three TI states during the first interrupt acknowledge cycle. During the second interrupt acknowledge cycle, five TI states are inserted in the bus cycles of both microprocessors. Both the  $\mu$ PD70108 and  $\mu$ PD70116 read an 8-bit vector during the second interrupt acknowledge cycle.

The number of cycles required to save the contents of the PSW, PS, and PC are different for the two microprocessors. This is because the width of the  $\mu$ PD70108 data bus is smaller than that of the  $\mu$ PD70116. Two bus cycles are required for the  $\mu$ PD70108 to read the offset word and segment word. Two bus cycles per word are also required to save the PSW, PS, and PC. The  $\mu$ PD70116 performs each of these operations in one bus cycle. The  $\mu$ PD70116 UBE signal remains low during the first and second interrupt acknowledge cycles and during the subsequent accessing of the offset and segment words.

## **BRK FLAG (SINGLE-STEP INTERRUPT)**

The  $\mu$ PD70108/70116 is provided with a single-step interrupt function that is useful for program debugging. The Break Flag (bit 8 of the PSW) controls this interrupt. There is no instruction that directly sets or resets the BRK flag; therefore, the PSW must be saved from the stack to control the BRK flag. By restoring the contents of the PSW from the stack, the BRK flag can be set or reset by using OR and AND instructions on the PSW in the stack. When the BRK flag is set, an interrupt routine specified by vector 1 starts after the current instruction has been executed. The BRK and interrupt enable (IE) flags are also reset at this point.

The debug program checks the number of single steps while the interrupt routine is being executed. If the singlestep operation can be terminated, a memory operation instruction resets the BRK flag that is saved in the stack. The program then returns to the main routine and the next sequence of instructions is successively carried out. If the program returns to the main routine without changing the BRK flag, the BRK flag (1 in the PSW) will be restored from the stack. The program then executes one instruction of the main routine and the vector 1 interrupt occurs again.

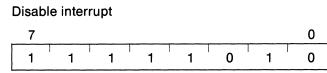

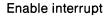

## INTERRUPT DISABLE TIMING

NMI and INT interrupts are not acknowledged when

An instruction that directly sets data in the segment register is being executed; for example

MOV sreg, reg16 MOV sreg, mem16

• The program is between one of the following and the next instruction

MOV sreg, reg16 MOV reg16, sreg MOV sreg, mem16 MOV mem16, sreg POP sreg

Program execution is between one of the following three types of prefix instructions and the next single instruction

Segment override prefix (PS:, SS:, DS0:, DS1:) Repeat prefix (REPC, REPNC, REP, REPE, REPZ, REPNE, REPNZ) Bus lock prefix (BUSLOCK)

Program execution is between the El instruction and the next instruction (INT only)

Only an NMI request signal generated during the above interrupt disable timing will be internally retained. The request will be acknowledged on completion of the subsequent single instruction.

#### INTERRUPTS DURING BLOCK INSTRUCTIONS

If an external interrupt (NMI or INT with interrupts enabled) occurs while a primitive block transfer, comparison, or I/O instruction is being executed, the CPU will acknowledge the interrupt and branch to the interrupt address. At the beginning of the interrupt routine, the contents of the CW register (a counter for block data) will be saved to the stack. After the contents of the CW have been restored at the end of the interrupt routine, the execution of the CPU will be returned to the original routine. In this manner, the interrupted block operation is resumed.

If prefix instructions have existed before the block operation instruction, up to three will be retained.

When the program returns from the interrupt routine, execution must return to the address at which the prefix instruction is held. For this reason, the  $\mu$ PD70108/70116 modifies the return address (minus one address per prefix instruction) when it is saved.

To best use the  $\mu$ PD70108/70116, do not place more than three prefix instructions before a block operation instruction.

**Correct Example:**

BUSLOCK

REPC

NMI → CMPBKB SS: src-block, dst-block

In the correct example, the BUSLOCK, REPC, and SS instructions are executed when program execution has been returned from the NMI interrupt process.

Incorrect Example:

BUSLOCK

REP

REPC

NMI  $\rightarrow$  CMPBK SS: src-block, dst-block

In the incorrect example, only the REP, REPC, and SS instructions will be executed when the program returns from the NMI interrupt process. Since more than three prefix instructions were placed before the block operation instruction, program execution incorrectly returns to the REP instruction instead of the BUSLOCK instruction.

To reset and initialize the  $\mu$ PD70108/70116, a positive pulse must be present on the RESET pin for at least four clock periods.

A CPU reset signal initializes the  $\mu$ PD70108/70116 as follows.

- Clears the following registers to 0000H.

PFP (prefetch pointer)

PC (program counter)

SS (stack segment)

DS<sub>0</sub> (data segment 0)

DS<sub>1</sub> (data segment 1)

- Sets PS (program segment) register to FFFFH

- Flushes the instruction queue

- Sets or resets the following PSW (program status word( flags: MD = 1 (native mode)

DIR = 0 (address direction used during block transfer, Autoincrements) IE = 0 (INT disabled) BRK = 0 (single-step interrupt disabled)

All other registers are undefined.

After the reset signal returns to the low level, the CPU begins execution of the program starting at address FFFF0H.

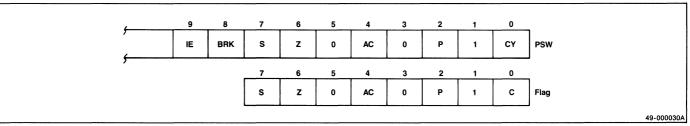

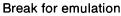

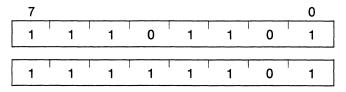

The  $\mu$ PD70108/70116 has two CPU operating modes: native and 8080 emulation. In native mode, the  $\mu$ PD70108/70116 executes all the instructions given in Section 12, with the exception of the RETEM and CALLN instructions. In 8080 mode, the microprocessor executes the instruction set for the  $\mu$ PD8080AF and the RETEM and CALLN instructions. These modes are selected by special instructions or by using an interrupt. The most significant bit of the PSW is a mode (MD) flag that controls mode selection.

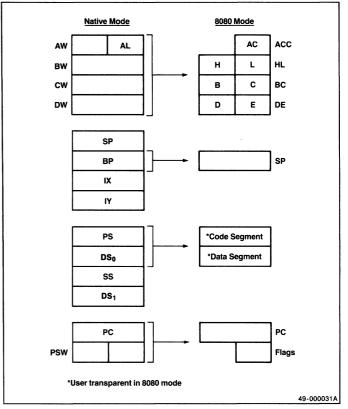

## NATIVE AND 8080 MODE SHIFTING

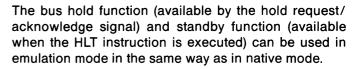

When the operating mode is changed from native to emulation or vice versa, the registers will be mapped into the emulation mode as shown in figure 8-1. The lower eight bits of the AW register and both the lower and higher eight bits of the BW, CW, and DW registers of the  $\mu$ PD70108/70116 serve as the accumulator and six general-purpose registers of the  $\mu$ PD8080AF. Figure 8-2 shows the lower eight bits of the PSW of the  $\mu$ PD70108/70116 serving as  $\mu$ PD8080AF flags. These flags correspond to the lower eight bits of the PSW.

The SP register serves as the stack pointer of the  $\mu$ PD8080AF in native mode while the BP register acts as the stack pointer in the emulation mode. In this way, the  $\mu$ PD70108/70116 employs independent stack pointers and stack areas in each mode. Using independent stack pointers prevents destruction of the contents of a stack pointer in one mode due to misoperation of the stack pointer in the other mode. The AH, SP, IX, and IY registers and the four segment registers (PS, SS, DS<sub>0</sub>, DS<sub>1</sub>) are not addressable from emulation mode.

In emulation mode, the segment base of the program is determined by the PS register whose contents have been specified by an interrupt vector before the CPU entered emulation mode. The segment base of the memory operands (including the stack) is determined by the  $DS_0$  register whose contents the programmer specifies before the CPU enters emulation mode.

Figure 8.2. Corresponding PSW and Flags

The  $\mu$ PD70108/70116 operates in terms of its normal BCU hardware even in emulation mode. Therefore, I/O operations between the  $\mu$ PD70108/70116 and peripheral circuits or memory are exactly the same as those performed in native mode. However, the BUSLOCK and POLL functions are unavailable for use in emulation mode.

#### Figure 8.1. Corresponding Registers

To determine externally if the  $\mu$ PD70108/70116 is in emulation mode, confirm that the processor status PS<sub>3</sub> signal output during a  $\mu$ PD70108/70116 bus cycle has become high. This signal is always at a low level in native mode. Figure 8-3 shows the mode shift operation of the CPU.

The CPU can reenter emulation mode when INT is present (even if interrupts are disabled) and restart program execution beginning with the instruction after the HLT instruction. This is true only if the CPU entered the standby mode from emulation mode.

If RESET or NMI is present instead of INT — or if INT is present while interrupts are enabled — the CPU will enter native mode from standby mode. If this happens, the CPU can reenter emulation mode from native mode; in other words, from the NMI or INT interrupt routine in native mode, through execution of the RETI instruction. If the CPU entered standby mode from native mode, the CPU can reenter native mode by inputting RESET, NMI, or INT regardless of whether interrupts are disabled or enabled.

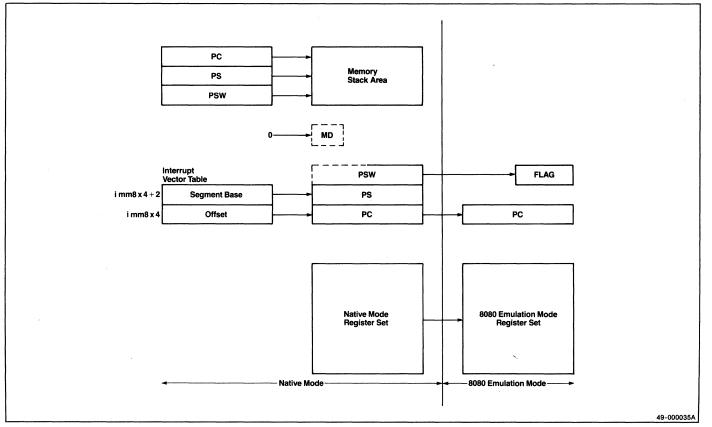

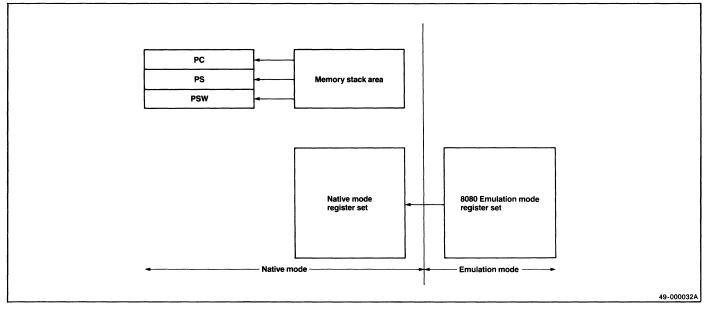

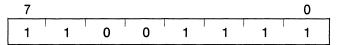

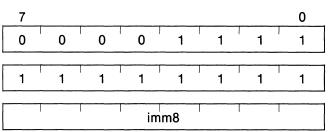

Two instructions cause the operating mode to be changed from native the 8080 emulation mode. These instructions are BRKEM (break for emulation) and RETI (return from interrupt).

#### **BRKEM imm8 Instruction**

The BRKEM instruction starts the 8080 emulation mode. It saves the contents of the PSW, PS, and PC, and resets the MD flag to 0. The segment base and offset values are then loaded into the PS and PC registers respectively from the interrupt vector table. The interrupt vector number is specified by the immediate operand of the BRKEM instruction.

When the 8080 emulation mode is started by the BRKEM instruction (MD = 0), the CPU executes the program in the 64 Kbyte segment area specified by the contents of the PS, starting from the address indicated by the con-

Figure 8-5.

tents of the PC. The instruction code fetched at this point is interpreted as the  $\mu$ PD8080AF instruction and is executed (figure 8-4).

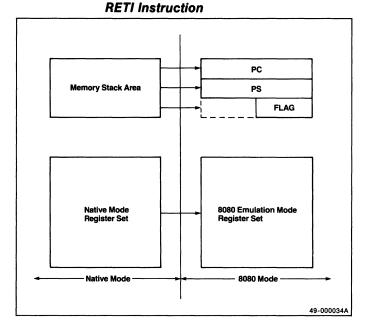

#### **RETI Instruction**

The RETI instruction is generally used when returning program execution to the main routine from an interrupt routine started by an external interrupt or BRK, or CALLN instruction. When the RETI instruction restores the contents of the PSW, PS, and PC, it also restores the status of the mode (MD) flag before the mode was changed from 8080 to native. This restored MD flag allows the CPU to be returned to the emulation mode again (figure 8-5).

For this reason, if the RETI instruction is executed in native mode at the end of the interrupt routine that has been started by the interrupt instruction CALLN, or by an external interrupt while the CPU is in 8080 mode, the CPU can reenter 8080 mode.

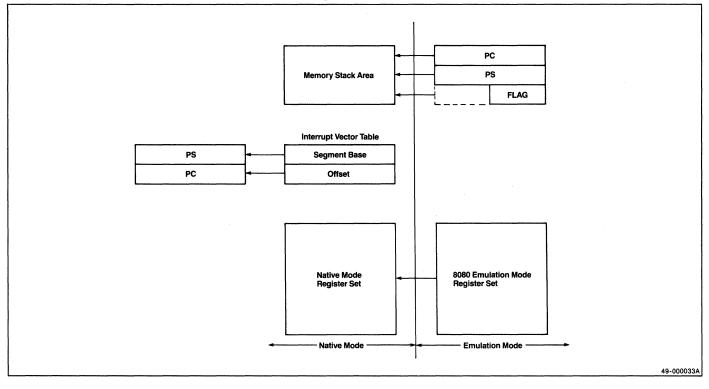

## 8080 EMULATION TO NATIVE MODE

The following signals and instructions are used to change the operating mode from 8080 to native.

- RESET

- NMI or INT

- CALLN (call native)

- RETEM (return from emulation)

Figure 8-4. Shift from Native to 8080 Emulation Mode Using BRKEM Instruction

Shift from Native to 8080 Mode Using

#### **RESET Operation**

When the RESET signal is present, a reset operation is performed on the CPU the same as in native mode. The 8080 emulation in progress is aborted.

#### **NMI or INT Operation**

When the NMI or INT signal is present, the interrupt process is performed the same as in native mode. Program execution of the CPU will return to the main routine from the interrupt routine in native mode. From native mode, the CPU can reenter the 8080 emulation mode by executing the RETI instruction (figure 8-6).

#### **CALLN Instruction**

The CALLN instruction is used exclusively in the emulation mode when calling a native mode subroutine not written in 8080 code. If the CALLN instruction is executed in 8080 mode, it causes the CPU to save the contents of the PS, PC, and PSW, and sets the mode flag to 1. This instruction also loads the segment base of an interrupt vector to the segment register (PS) and the offset to the program counter (PC) (figure 8-6).

When the RETI instruction is executed at the end of the interrupt routine, program execution can be returned to the main routine in 8080 emulation mode from the interrupt routine in native mode started by the CALLN instruction.

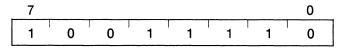

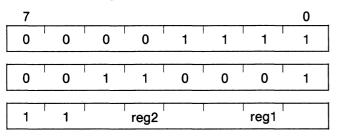

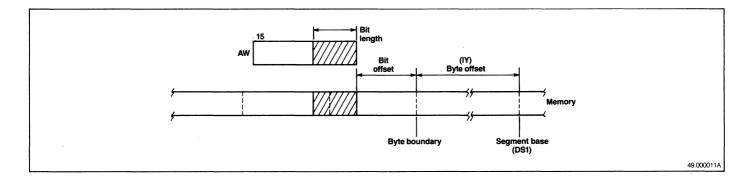

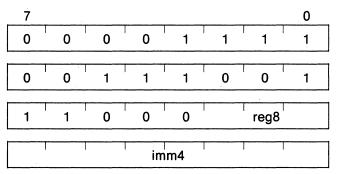

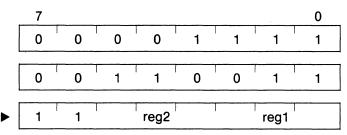

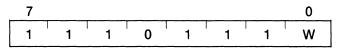

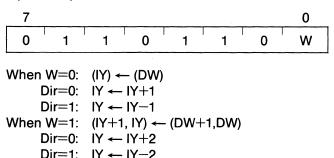

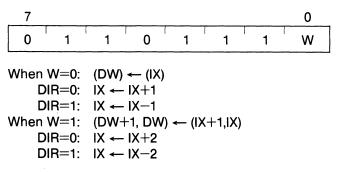

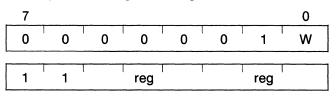

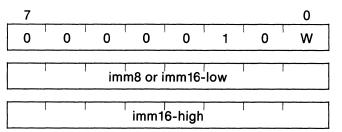

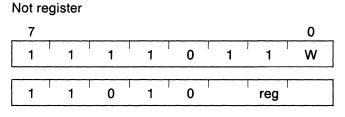

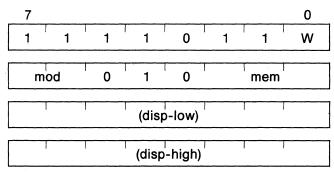

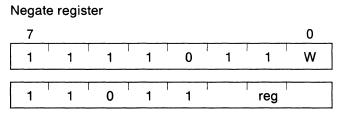

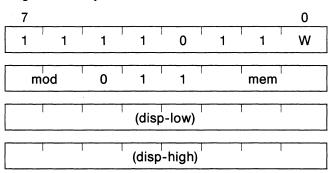

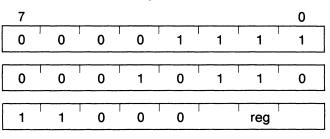

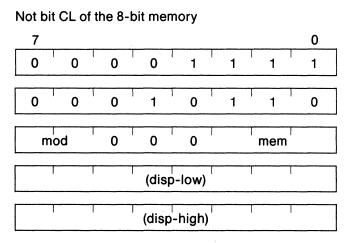

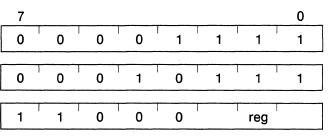

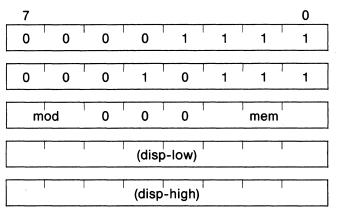

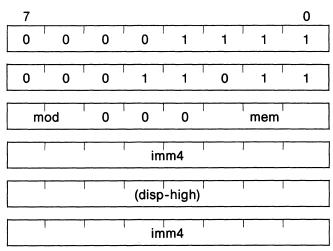

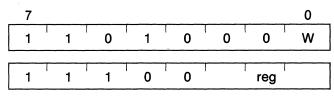

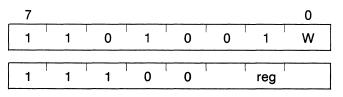

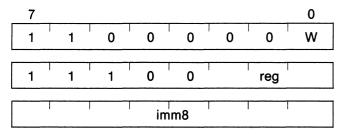

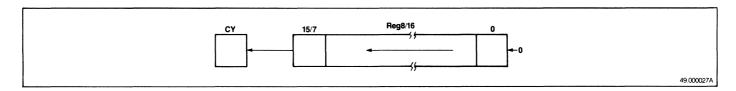

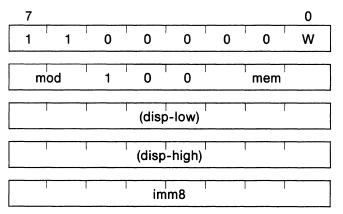

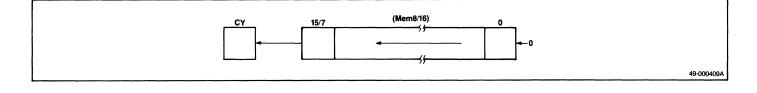

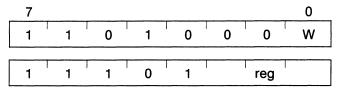

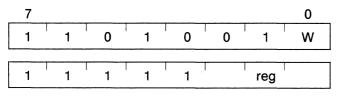

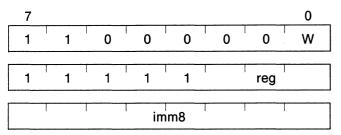

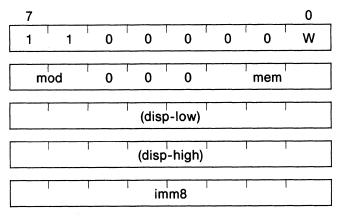

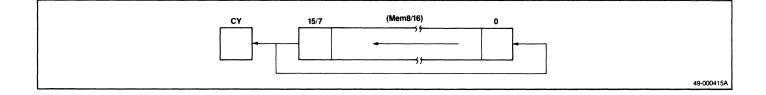

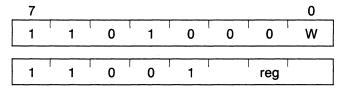

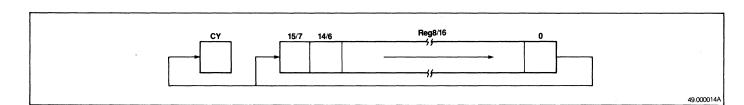

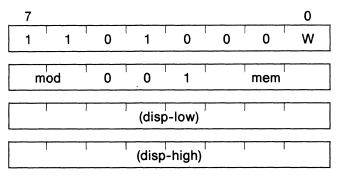

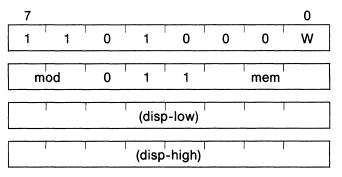

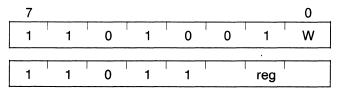

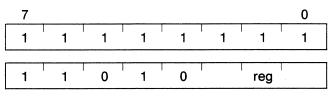

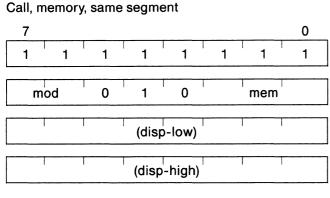

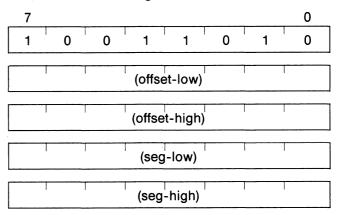

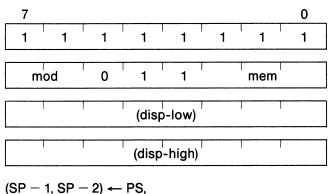

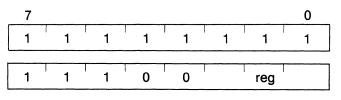

#### **RETEM Instruction**