# Der NDR-Klein Computer

#### ELEKTRONIKLADEN

Mikrocomputer GmbH & Co. KG

4930 DETMOLD 18

## Gebrauchs- und Aufbauanleitung

### Speicher-Baugruppe DRAM 128k

Die DRAM 128K wurde entwickelt, um die Anschaffung großer Speicher, wie sie beispielsweise für die Erstellung Übersetzung großer Pascal-Programme oder durch den Einsatz einer Floppy nötig werden, preiswert zu ermöglichen. Da dynamische Speicherzellen, wie sie auf dieser Speicherkarte verwendet werden, nur beim Lesen und beim Schreiben Strom aufnehmen, liegt die Verlustleistung erheblich unter der von statischen RAMs. Dies bedeutet auch, daß die Integrationsdichte und damit die Speicherkapazität pro Chip erhöht werden konnte. was wiederum die Kosten gegenüber statischen RAMs senkt. Die Karte ist an den Betrieb mit den Prozessoren 6,8008 und Z80 angepaßt. Beim Z80 müssen jedoch alle Adreßleitungen auf den Bus geführt sein, wie es bei der Vollausbau-CPU der Fall ist. Außerdem muß eine Schaltung der Adreßerweiterung vorhanden sein (Bank Boot-Karte), da der Z80 lediglich 64K-byte adressieren kann. Die DRAM 128k beherbergt 128k-byte RAM, kann allerdings auch teilbestückt, d.h. mi 64k-byte, betrieben werden.

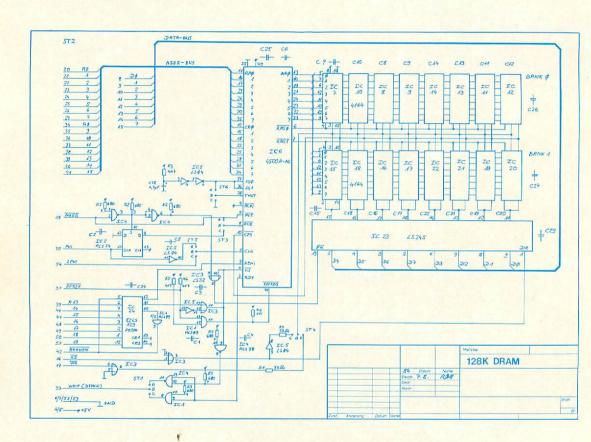

## Schaltplan

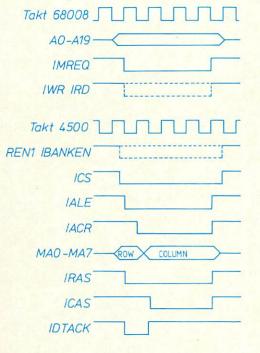

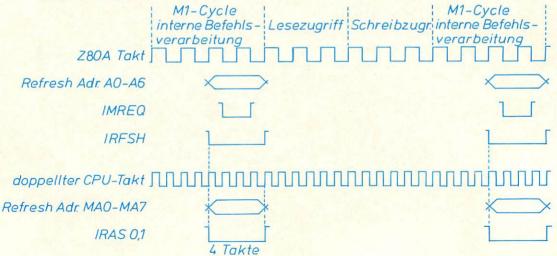

Impulsdiagramm, Speicherzugriff des 68008 zwischen zwei Refresh-Zyklen.

## **Aufbauanleitung**

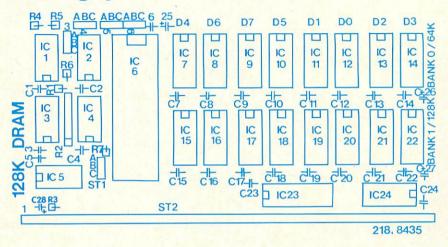

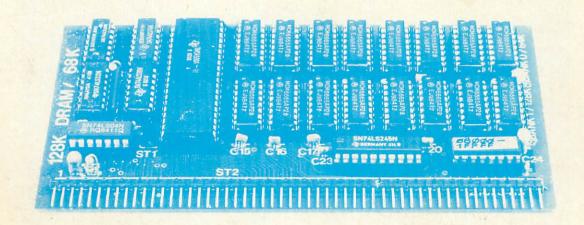

Beginnen Sie mit dem Einlöten des Bussteckers. Die Anschlußstifte sollten parallel zur Leiterplatte ausgerichtet sein, damit diese später gerade im Bus steckt. Die Bestückungsseite ist am gelben Bestückungsaufdruck erkennbar. Danach können die IC-Fassungen eingelötet werden. Die Fassungen sollten so eingelötet werden, daß sich die Pinl-Markierung der Fassung (meist ist die Fassung hier etwas abgeschrägt) später mit Pinl des IC deckt. Das erschwert ein falsches Einstecken der ICs. Bitte vergewissern Sie sich auch immer, daß die Größe der Fassung stimmt, denn eine einmal eingelötete Fassung zu entfernen, ist immer eine heikle Arbeit. Neben der Fassung für das PROM (IC24) sind zwei Durchkontaktierungen. Die Fassung muß ganz zum Plattenrand, so daß die Durchkontaktierungen frei bleiben. Nun werden die Kondensatoren eingelötet. C1-C24 sind 100nF-Typen (Aufdruck 100n oder 104). Sie verhindern Spannungseinbrüche in den Versorgungsspannungen der ICs, wie sie beim Schalten von hohen kapazitiven Lasten entstehen können. C25-C28 sind Tantalkondensatoren, die unbedingt richtig herum eingelötet werden müssen. Der + Anschluß ist am Kondensator und auf der Leiterplatte markiert. Sie dienen bis auf C28 ebenfalls zur Beruhigung der Betriebsspannung. C28 ist Bestandteil der Reset-Logik. Die Widerstände Rl.R7 (orange, orange, schwarz), R3, R5, R6 (gelb, lila, rot) und R4 (braun, schwarz, rot) werden stehend eingelötet. Der aufgedruckte Punkt am Widerstandsnetzwerk R2 (6x680 Ohm) muß in Richtung IC5 zeigen. Schließlich müssen noch die Brücken STl und ST3 - ST6 eingelötet werden. Nachdem Sie alle überstehenden Drahtenden abgeschnitten haben, kontrollieren Sie nochmals alle Lötstellen. Mit einem Widerstandsmeßgerät kann die Karte auf Kurzschlüsse in der Betriebsspannung überprüft werden. Dazu sollte die + Leitung des Ohmmeters (bei Vielfachmeßgeräten in der Regel der mit - gekennzeichnete Anschluß) mit + der Speicherkarte, und die - Leitung entsprechend mit Masse. verbunden werden. Wählen Sie den Meßbereich xlk. Ist die Karte in Ordnung, darf das Ohmmeter nicht ausschlagen. Nun kann die Karte in den Bus gesteckt werden. Nachdem die Spannung ein-

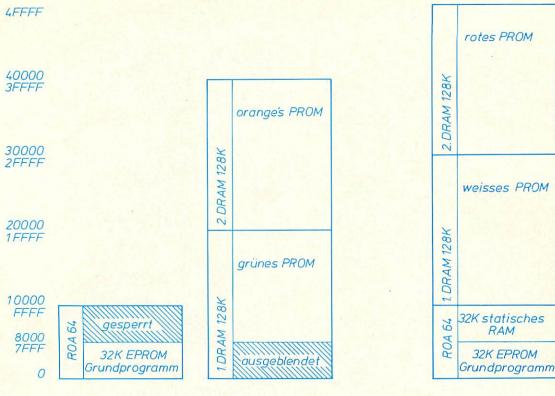

Möglichkeiten zur Speichergestaltung

Multiplex genannt. Zur Richtungsumschaltung besitzen die Speicher den Anschluß /WR, der im 68008-Betrieb mit R/W (Busleitung /WR) verbunden ist. Beim Z80 wird das invertierte /RD Signal zur Umschaltung benutzt, weil es früher als das /WR Signal erscheint.

Dies ist notwendig, weil die Richtung feststehen muß, bevor der Speicher komplett adressiert ist (Early-Write-Betrieb), also bevor /CAS aktiv wird.

Early-Write-Betrieb ist die Voraussetzung für das Zusammenschalten der Datenein- und -ausgänge. Die Richtungsumschaltung des Datenbustreibers schließlich erfolgt durch /RD. Folgendes Diagramm zeigt einen Speicherzugriff des 68008 mit allen wesentlichen Signalen. Zur Bestimmung der genauen Schaltzeiten sind die entsprechenden Datenblätter der Bauteilehersteller heranzuziehen.

#### Adressierung und Speicherzugriffe

Sobald der Prozessor einen Speicherzugriff einleitet. legt er zuerst eine Adresse auf den Bus. Auf diese Adresse dürfen nur 8 Speicherzellen (1 Byte) reagieren. Alle anderen Speicherzellen müssen vom Datenbus abgeschaltet bleiben, um Störungen zu vermeiden. Die DRAM 128k darf auf maximal 131072 (128k) verschiedene Adressen reagieren. Welche Adressen dies sind, wird durch eine Adressierlogik festgelegt, die hier im wesentlichen aus einem PROM besteht. Ein PROM ist in seiner Funktion einem EPROM vergleichbar. Es ist allerdings nicht löschbar, dafür aber wesentlich schneller. Auf der DRAM 128K kommt ein PROM mit acht Adreßeingängen und vier Datenausgängen zum Einsatz. Die Adreßeingänge sind mit Al3 - Al9und /Banken belegt. Es überstreicht den ganzen Adrefraum des 68008 von 0 - 1Mbyte in 8kbyte-Schritten (Al3), verarbeitet das Signal /Banken und aktiviert die Datenausgänge entsprechend der Programmierung. Der wichtigste Datenausgang ist der /CS-Ausgang (Pin 11), der bei jeder gültigen Adresse den TMS 4500 mit Speichern und Waiterzeugung und den Datenbustreiber (IC23) freigibt. Ausgang 12 enthält die Information über die anzusteuernde 64k-Bank und steuert den Eingang REN1 des 4500. Ausgang 10 ermöglicht über die Leitung /Banken die Sperrung von Speicherbereichen auf anderen Speicherkarten (in 8 kbyte Schritten). Dank dieser universellen Möglichkeiten wird ein überlappender Einsatz mit anderen Speicherkarten ermöglicht. Doppelt vorhandene Speicherbereiche lassen sich entweder auf der anderen Speicherkarte sperren oder auf der DRAM 128k ausblenden. So kann z.B. der 68008 vollkommen ohne statische RAMs betrieben werden.

Ist eine angelegte Adresse für diese Karte gültig, so ist der Speicher über /CS freigegeben und über REN1 ist die entsprechende Speicherbank festgelegt. Sofern gerade ein Refreshzyklus läuft, wird über RDY (Ready) die Leitung /WAIT solange auf L-Signal gesetzt, bis die Speicher wieder frei sind. Alle Prozessorausgänge verharren solange in ihrem augenblicklichen Zustand. Sobald der Prozessor wieder freigegeben ist, werden die Adressen AO-A7 sofort über MAO-MA7 an die Speicher gelegt. Kurz darauf folgt, in Abhängigkeit von REN1, das Zeilenübernahmesignal /RASO oder /RAS1. Damit steht die Zeilenadresse im Speicher und wird dort solange gehalten, wie /RAS auf L-Signal liegt. Kurz nach der Adresse gibt der Prozessor das Signal /MREQ aus. Es ist im Z80 -Betrieb parallel auf die Eingänge /ALE (Zwischenspeicherfreigabe) und /ACR (Lesezugriff) des TMS 4500 geschaltet (ST3) und veranlaßt die Abschaltung der Zeilenadresse durch das Anlegen der Adressen A8-A15 als Spaltenadressen über die Anschlüsse MAO -MA7 an die Speicher. /RAS bleibt während des gesamten Zugriffes auf L-Signal.

Im 68008-Betrieb erscheint /MREO so früh. daß die Zeilenadresse zu kurz an den Speicherchips anliegen würde. Es wird deshalb über einen Flipflop um eine halbe Taktperiode verzögert, bevor es auf /ACR wirkt. Damit wird das Abschalten der Zeilenadresse und das Anlegen der Spaltenadresse um diese Zeit verzögert. Kurz nach der Spaltenadresse erscheint das Spaltenübernahmesignal /CAS, das zusammen mit der Spaltenadresse einer Spalte alle 8 Chips einer Bank freigibt. Da die Zeilen schon freigegeben sind, ist in allen ICs je ein Bit angesprochen. Die Daten können nun eingeschrieben oder ausgelesen werden. Die Übertragung der Adressen A0-A15 nacheinander in zwei Hälften über dieselben Leitungen (MA0-MA7) wird

Da die Zykluszeiten der verwendeten Speicherbausteine für einen synchronen Betrieb des 68008 zu lang sind, wird während eines Speicherzugriffs grundsätzlich ein Waitzyklus eingefügt, der den Prozessor kurzzeitig anhält und so den Speichern genügend Zeit gibt, die Daten zur Verfügung zu stellen. Im Z80-Betrieb wird das Signal /RFSH des Prozessors zur Synchronisation zwischen CPU und DRAM-Steuerbaustein benutzt. Dieses Signal liefert die CPU in der zweiten Hälfte jedes Befehlslesezyklus, also dann, wenn nicht mehr gelesen, sondern intern verarbeitet wird. Dazu ist der/RFSH Ausgang des Z80 mit dem /REFREQ Eingang des 4500 verbunden. Mit jeder fallenden Flanke an /REFREO wird der Auffrischzähler um eine Zeilenadresse weitergeschaltet und der Refresh-Zeitgeber wird zurückgesetzt. Sollten über einen langen Zeitraum keine /RFSH-Signale vom Prozessor kommen, wird dies vom Refresh-Zeitgeber erkannt und die Auffrischung wird mit der durch FSO,FS1 und TWST eingestellten Frequenz fortgesetzt. Die Refreshzyklusdauer beträgt in jedem Fall vier Taktperioden. Da die vom Prozessor abgegebene Auffrischadresse nicht zu einem Speicherzugriff führen darf.wird der Freigabeeingang /CS des TMS 4500 mit //RFSH verriegelt. Um mit einem Refreshzyklus nicht in den nächsten Speicherzugriff des Prozessors zu geraten, was mit 4 MHz Taktfreguenz und 4 Takten pro Refreshzyklus passieren würde, ist der doppelte CPU Takt notwendig, der über Busleitung 54 (Reserve) von der Vollausbau CPU (CPUZ80) übertragen wird.

In dieser Konfiguration ist ein Betrieb ohne Waits möglich, da zum einen keine Zugriffe während eines Refresh-Zyklus stattfinden und zum anderen die Speicherzugriffszeiten für den 280 ausreichend sind.

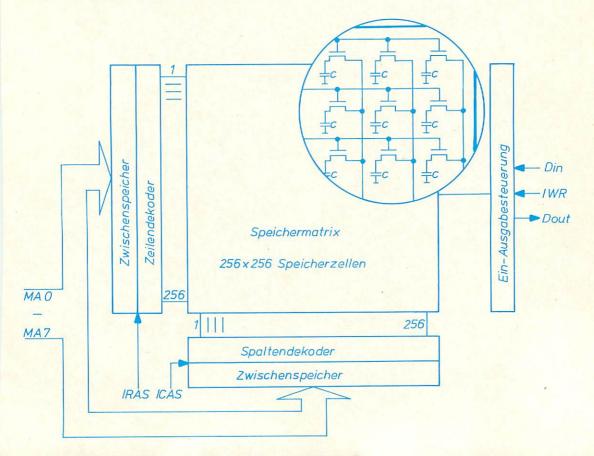

Jeder Baustein verfügt über einen Dateneingang (DIN) und einen Datenausgang (DOUT). Es kann also nur ein Bit pro Adresse eingeschrieben bzw. ausgelesen werden. Man spricht daher auch von einer Speicherorganisation 64kxl. Da sich beim NDR-Klein-Computer ein Datenwort aus 8 Bit zusammensetzt, müssen die Speicherbausteine so geschaltet werden, daß pro Adresse ein Bit für jede Datenleitung vorhanden ist. Dieses wird durch adreßmäßiges Parallelschalten von 8 Chips realisiert. Die Speicherkapazität der so entstandenen Bank ist also 64k-byte. Auf der DRAM 128K sind zwei solcher Bänke untergebracht. In dynamischen Speicherstellen wird die Information in Kondensatoren gespeichert, die beim Schreiben aufgeladen werden und deren Ladung nur eine begrenzte Zeit aufrecht erhalten weden kann. Es ist notwendig sie in regelmäßigen Abständen nachzuladen. Die maximalen Abstände betragen 2ms bei den Chips mit 128 Zeilen und 4ms bei denen mit 256 Zeilen (1ms= 1 tausendstel Sekunde). Eine Vereinfachung des Refresh (Aufladung, Auffrischung) ergibt sich dadurch, daß beim Zugriff auf ein Bit jeweils die gesamte Zeile aufgefrischt wird. Somit sind also 128 bzw. 256 Zugriffe für einen Refresh notwendig. Diese Aufgabe übernimmt der "Dynamic RAM Controller" TMS 4500A, ein integrierter Auffrischzähler, der fortlaufend die Zeilen 1 - 256 adressiert.

Die Adresse wird über die Anschlüsse

MAO - MA7 an alle Speicher gelegt. Kurz

darauf werden über die Anschlüsse

/RASO und /RASI (Zeilenübernahmesignale), die während einer Auffrischung

parallel geschaltet sind, die Anschlüsse

/RAS sämtlicher Speicherchips aktiviert.

Damit wird die Zeilenadresse an die

Speicher übernommen, wo sie dekodiert

und der entsprechenden Zeile zugeordnet

wird. Alle Speicherbausteine werden

gleichzeitig aufgefrischt.Da der Adreßdekoder in den Speichern mit 128 Zeilen

nur 7 Bit dekodieren kann ( 2 hoch 7 = 128), fängt für ihn ab Zeilenadresse 129 wieder ein neuer Zyklus an, der damit nur halb so lang ist, wie der bei den 256-zeiligen. Der DRAM-Controller TMS 4500A bezieht seinen Arbeitstakt aus dem korrespondierenden Prozessorsystem. Zur Anpassung an verschiedene Systeme dienen die Eingänge FSO. FSI und TWST, die gleichzeitig Reseteingänge sind.

|        | Eingänge |     |     |       | Refresh  | Takte pro      |

|--------|----------|-----|-----|-------|----------|----------------|

|        | TWST     | FS1 | FS0 | Waits | Frequenz | Refresh-Zyklus |

|        | L        | L   | L   | Reset |          |                |

|        | L        | L   | H   | 0     | Takt:31  | 3              |

|        | L        | H   | L   | 0     | Takt:46  | 3              |

| Z-80-  | L        | H   | H   | 0     | Takt: 61 | 4              |

|        | H        | L   | L   | 7     | Takt: 46 | 3              |

|        | H        | L   | H   | 7     | Takt:61  | 4              |

|        | H        | H   | L   | 1     | Tokt:76  | 4              |

| 68008- | H        | H   | H   | 1     | Takt:91  | 4              |

Diese Eingänge sind so zu beschalten. daß der TMS 4500A beim Einschalten der Spannung einen Reset erhält, um alle internen Zähler und Register in einen definierten Zustand zu versetzen. Eine eigene Reset-Logik ist notwendig durch die lange Resetzeit des 68008, die größer als 100ms sein muß. Anderen Falles wären, würde ein Program mit Reset abgebrochen, die auf der DRAM128K gespeicherten Daten verloren, da während des Resets die Auffrischung unterbrochen wird. Außerdem müssen die durch den Prozessor vorgegebenen zeitrelevanten Bedingungen, wie Taktfrequenz und Zugriffszeiten, an die Eigenschaften der Speicherbausteine, die durch Refreshintervallzeiten (2ms oder 4ms) und Speicherzugriffszeiten vorgegeben sind, angepaßt werden. Hier muß grundsätzlich zwischen 68008- und Z80-Betrieb unterschieden werden.

Im 68008-Betrieb ist die Brücke ST6 so gesteckt, daß sich eine Auffrischfrequenz von Takt :91. also 88 kHz und eine Refreshzyklusdauer von 4 Taktzyklen, also 0.5 us (Mikrosekunden),ergibt.

#### Schaltungsbeschreibung

Speicher und Refresh Die auf der DRAM 128k verwendeten Speicherchips vom Typ 4164, 8264, 6665 etc setzen sich aus je 65536 (64k-bit) dynamischen Speicherzellen zusammen, die je nach Fabrikat in einer Matrix (Art der Anordnung) von 128x512 oder 256x256 angeordnet sind. Das Bild zeigt eine vereinfachte Darstellung eines Chips mit 256 Zeilen und 256 Spalten.

#### Bestückungsplan

#### Stückliste

| IC 1             | 74ALS09    | Int. Schaltung      |

|------------------|------------|---------------------|

| IC 2             | 74ALS74    | Int. Schaltung      |

| -IC 3            | 74 LS32    | Int. Schaltung      |

| IC 4             | 74ALS38    | Int. Schaltung      |

| -IC 5            | 74LS04     | Int. Schaltung      |

| IC 6 65 -        | TMS 4500A  | Int. Schaltung      |

| IC 7 - 22 /82    | 4164       | Int. Schaltung      |

| IC 23            | 74LS245    | Int. Schaltung      |

| IC 24            | PROM82S129 | Int. Schaltung      |

| R 1, R 7         | 33 Ohm     | Widerstand          |

| R 2              | 6x680 Ohm  | Widerstandsnetzwerk |

| R 3, R 5, R 6    | 4K7 Ohm    | Widerstand          |

| R 4              | 1K Ohm     | Widerstand          |

| C 1 - C 24       | 100nF      | Keram. Kondensator  |

| C 25             | 47 uF      | Tantal Kondensator  |

| C 26 - C 28      | 4.7uF      | Tantal Kondensator  |

| ST 1, 3, 4, 5, 6 | 3 pol.     | Stiftleiste         |

| ST 2             | 54 pol.    | abgew. Stiftleiste  |

| 5                |            | Kurzschlußstecker   |

| 5                |            | Leiterplatte        |

|                  |            |                     |

geschaltet worden ist, werden die Betriebspannungen der ICs gemessen. An ICl - IC5 liegt + an Pin14 und - an Pin7.

An IC7 - IC22 liegt + an Pin7 und - an Pin16. Bei IC23 liegt + an Pin20 und - an Pin10. Bei IC24 liegt + an Pin16 und - an Pin8.

Einzelne Funktionen lassen sich auf der DRAM 128k schlecht austesten. Deshalb ist es sinnvoller, die Funktionen der komplett bestückten Karte mit dem Betriebsprogramm des Prozessors zu überprüfen. Bevor die ICs eingesteckt werden, entladen Sie sich bitte über einen geerdeten Gegenstand. Die ICs lassen sich leichter einstecken, wenn die Beinchen auf einer geraden Unterlagen etwas angewinkelt worden sind.

Zum Schluß sind die Brücken STl und ST3-ST6 und das PROM entsprechend der Verwendung zu stecken. Sollte die Karte nicht funktionieren, machen Sie noch einmal eine gründliche Sichtkontrolle, denn die häufigsten Fehler lassen sich mit dem Auge (und einer Lupe) erkennen. Dies sind Lötbrücken, kalte Lötstellen, falsch gesteckte ICs oder abgeknickte Beinchen. Fehler in Bauelementen treten äußerst selten auf.

Ist nichts erkennbar, dann hilft die Meßtechnik weiter. Überprüfen Sie bitte ob der Takt an Pinl des TMS 4500A anliegt. Außerdem muß an Pin4 sämtlicher Speicherchips das /RAS-Signal zu messen sein. Der Verlauf weiterer Messungen hängt stark vom Verwenungszweck der Speicherkarte ab. Wird zum Beispiel die DRAM 128K ab Adresse \$ 8000 zusammen mit dem Grundprogramm der CPU 68k eingesetzt, adressiert der Prozessor, gesteuert vom Grundprogramm, laufend die Karte und aktiviert die Leitungen /RD. /WR und /MREO. Dies hat wieder Reaktionen des DRAM-Controllers zur Folge, die zu überprüfen sind. So kann mit Hilfe des Schaltpanes, der Schaltungsbeschreibung und eines Oszilloskops ein eventuell vorhandener Fehler eingegrenzt werden.

#### JUMPER

|      | 68008 | Z80   |

|------|-------|-------|

| ST 1 | В - С | В - С |

| ST 3 | в - С | A - B |

| ST 4 | A - B | В - С |

| ST 5 | A - B | В - С |

| ST 6 | A - B | B - C |

Bitte achten Sie darauf, daß Sie die ICs richig herum in die entsprechenden Fassungen stecken. Beachten Sie, daß das PROM mit Pinl nach rechts liegt.

El./Oct: 05232/8171

#### **Hintergrund**

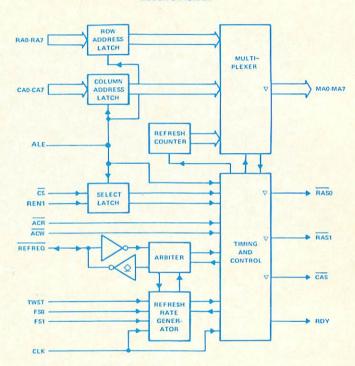

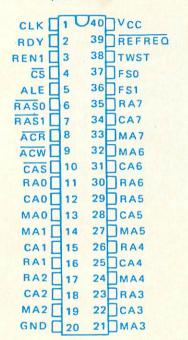

TMS4500A . . . NL PACKAGE

(TOP VIEW)

#### BLOCK DIAGRAM